电子商务的网站的建设内容深圳网站搭建哪里找

LeetCode 235. 二叉搜索树的最近公共祖先

1、题目

题目链接:235. 二叉搜索树的最近公共祖先

给定一个二叉搜索树, 找到该树中两个指定节点的最近公共祖先。

百度百科中最近公共祖先的定义为:“对于有根树 T 的两个结点 p、q,最近公共祖先表示为一个结点 x,满足 x 是 p、q 的祖先且 x 的深度尽可能大(一个节点也可以是它自己的祖先)。”

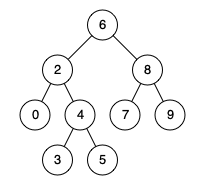

例如,给定如下二叉搜索树: root = [6,2,8,0,4,7,9,null,null,3,5]

示例 1:

输入: root = [6,2,8,0,4,7,9,null,null,3,5], p = 2, q = 8

输出: 6

解释: 节点 2 和节点 8 的最近公共祖先是 6。

示例 2:

输入: root = [6,2,8,0,4,7,9,null,null,3,5], p = 2, q = 4

输出: 2

解释: 节点 2 和节点 4 的最近公共祖先是 2, 因为根据定义最近公共祖先节点可以为节点本身。

说明:

- 所有节点的值都是唯一的。

- p、q 为不同节点且均存在于给定的二叉搜索树中。

2、递归

思路

代码

class Solution {

private:TreeNode* traversal(TreeNode* cur, TreeNode* p, TreeNode* q) {if (cur == nullptr) {return cur;}// 如果当前节点的值大于p和q的值,则在左子树中继续搜索if (cur->val > p->val && cur->val > q->val) {TreeNode* left = traversal(cur->left, p, q);// 如果在左子树中找到了符合条件的节点,则返回该节点if (left != nullptr) {return left;}}// 如果当前节点的值小于p和q的值,则在右子树中继续搜索if (cur->val < p->val && cur->val < q->val) {TreeNode* right = traversal(cur->right, p, q);// 如果在右子树中找到了符合条件的节点,则返回该节点if (right != nullptr) {return right;}}// 如果当前节点满足条件(即值介于p和q之间),则返回当前节点return cur;}

public:TreeNode* lowestCommonAncestor(TreeNode* root, TreeNode* p, TreeNode* q) {return traversal(root, p, q);}

};

复杂度分析

- 时间复杂度: O(n)

- 空间复杂度: O(n)

3、递归(精简版)

思路

代码

class Solution {

public:TreeNode* lowestCommonAncestor(TreeNode* root, TreeNode* p, TreeNode* q) {// 如果根节点的值大于p和q的值,说明p和q都在根节点的左子树中if (root->val > p->val && root->val > q->val) {// 递归调用左子树return lowestCommonAncestor(root->left, p, q);// 如果根节点的值小于p和q的值,说明p和q都在根节点的右子树中} else if (root->val < p->val && root->val < q->val) {// 递归调用右子树return lowestCommonAncestor(root->right, p, q);// 否则,根节点就是p和q的最低公共祖先} else return root;}

};

复杂度分析

- 时间复杂度: O(n)

- 空间复杂度: O(n)

4、迭代

思路

代码

class Solution {

public:TreeNode* lowestCommonAncestor(TreeNode* root, TreeNode* p, TreeNode* q) {while(root) {// 如果当前节点的值大于p和q的值,说明p和q都在当前节点的左子树中if (root->val > p->val && root->val > q->val) {root = root->left;// 如果当前节点的值小于p和q的值,说明p和q都在当前节点的右子树中} else if (root->val < p->val && root->val < q->val) {root = root->right;// 如果当前节点的值等于p或q的值,或者p和q分别在当前节点的左右子树中,那么当前节点就是最低公共祖先} else {return root;}}// 如果没有找到最低公共祖先,则返回nullptrreturn nullptr;}

};

复杂度分析

- 时间复杂度: O(n)

- 空间复杂度: O(1)