灰色项目网站代做中小型门户网站

列表与元组的区别

列表是动态数组,它们可变且可以重设长度(改变其内部元素的个数)。

元组是静态数组,它们不可变,且其内部数据一旦创建便无法改变。

元组缓存于Python运行时环境,这意味着我们每次使用元组时无须访问内核去分配内存。

深拷贝与浅拷贝的区别

浅拷贝只复制对象的第一层属性、深拷贝可以对对象的属性进行递归复制

浅拷贝基本类型的值之间互不影响,引用类型其中一个对象改变了地址,就会影响另一个对象;

深拷贝改变新对象不会影响原对象,他们之前互不影响。

浅拷贝:创建一个新对象,这个对象有着原始对象属性值的一份精确拷贝。如果属性是基本类型,拷贝的就是基本类型的值,如果属性是引用类型,拷贝的就是内存地址。

深拷贝:将一个对象从内存中完整的拷贝一份出来,从堆内存中开辟一个新的区域存放新对象

Python垃圾回收机制

python采用的是引用计数机制为主,标记-清除和分代收集两种机制为辅的策略。

(详情可查看http://t.csdn.cn/EHSjS)

web端与移动端测试区别

系统架构:web端是B/S架构,基于浏览器的。App项目是C/S架构,用户需要安装客户端。

性能:web端的性能更关注页面的响应速度,移动端更关注流量、耗电量、CPU、内存等

兼容性:web端更侧重于浏览器、电脑硬件、操作系统方面的兼容;移动端兼容的是手机设备,要看设备系统、机型、分辨率、屏幕尺寸。

交互方式:web主要采用鼠标点击方式;而App主要是手指点击、拖拽、手势测试、横屏测试,考虑更多的是手指的交互习惯。

web测试是基于浏览器的,所以不用考虑安装卸载。而App是客户端,必须测试安装、卸载、更新,还需要考虑其他异常情况,包括安装时候中断、弱网,安装后删除安装文件(可删除,不影响软件正常运行)。

selenium定位不到元素怎么办

要确认是哪种原因定位不到:

frame/iframe表单嵌套

页面跳转到新标签页,或弹出警告框等

页面元素失去焦点导致脚本运行不稳定

使用Xpath或CSS定位

页面还没加载出来就对页面上的元素进行操作

元素被遮挡,不可用,不可见

用WebDriver调用JavaScript代码代替无法实现的功能

解决办法详情可参考http://t.csdn.cn/wWq1P

服务器资源显示不足,用Linux命令怎么找到问题

通过执行以下命令,可以在1分钟内对系统资源使用情况有个大致的了解。

uptime

dmesg | tail

vmstat 1

mpstat -P ALL 1

pidstat 1

iostat -xz 1

free -m

sar -n DEV 1

sar -n TCP,ETCP 1

top

详情可以参考http://t.csdn.cn/GdgQh

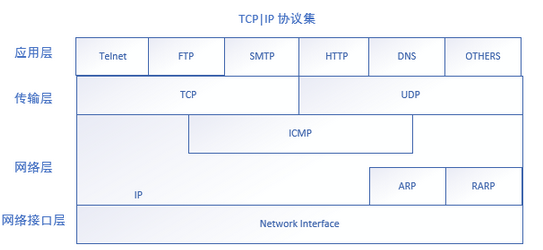

TCP/IP四层模型

从上到下依次是应用层,传输层,网络层,网络接口层(数据链路层)

TCP与UDP的区别

TCP 是面向连接的,UDP 是面向无连接的

UDP程序结构较简单

TCP 是面向字节流的,UDP 是基于数据报的

TCP 保证数据正确性,UDP 可能丢包

TCP 保证数据顺序,UDP 不保证

什么是面向连接,什么是面向无连接:在互通之前,面向连接的协议会先建立连接,如 TCP 有三次握手,而 UDP 不会TCP 为什么是可靠连接:通过 TCP 连接传输的数据无差错,不丢失,不重复,且按顺序到达。

TCP 报文头里面的序号能使 TCP 的数据按序到达

报文头里面的确认序号能保证不丢包,累计确认及超时重传机制

TCP 拥有流量控制及拥塞控制的机制

Http与Https的区别

HTTPS 协议需要到 CA (Certificate Authority,证书颁发机构)申请证书,一般免费证书较少,因而需要一定费用。

HTTP 是超文本传输协议,信息是明文传输,HTTPS 则是具有安全性的 SSL 加密传输协议。

HTTP 和 HTTPS 使用的是完全不同的连接方式,默认端口也不一样,前者是80,后者是443。

HTTP 的连接很简单,是无状态的。HTTPS 协议是由 SSL+HTTP 协议构建的可进行加密传输、身份认证的网络协议,比 HTTP 协议安全。(无状态的意思是其数据包的发送、传输和接收都是相互独立的。无连接的意思是指通信双方都不长久的维持对方的任何信息。)

理论上,http响应速度更快,这是因为http只需三次握手,也就是3个包即可建立连接, 而https除了三次握手,还需进行ssl握手,一共需要12个包。

https是构建在SSL之上的http协议,所以https会消耗更多的服务器资源。

用SQL查找平均分低于80分的学生学号

SELECT Sno, AVG(Score) AvgScore

FROM SC

GROUP BY Sno

HAVING AVG(Score)<80

算法1:用指针合并两个有序数组

arr1 = [1,3,4,6,10] #初始化两个数组

arr2 = [2,5,8,11]

ind = 0

ans = arr1.copy() #ans 初始化为 arr1

for i in range(0,len(arr2)):while ind < len(arr1):if arr2[i] <= arr1[ind]: #ind 的范围不能超过数组元素下标的最大值ans.insert(ind + i,arr2[i]) #向第一个数组中的合适位置插入第二个数组中的数breakelse:ind += 1 #如果 ind 指向的数比 i 指向的数小,则 ind 向后一位else: #如果 arr1 已遍历完,直接把剩下的 arr2 拼到 arr1 结尾ans = ans + arr2[i:]breakwhile...else 语句是用来判断 while 循环是否被完整执行完的语句。

如果 while 循环的结束是因为 while 后面的判断语句(ind < len(arr1))的返回值为 False,则执行 else;

如果是因为 break 而跳出循环,则不执行 else。

为什么要用 ans 存储 arr1 的值,而不在 arr1 内部直接改动呢?

如果直接使用 arr1 存储答案,在向数组中添加元素的过程中,列表内部的元素会变化,也就是说,我

们丢失了 arr1 的原来的值。用 ind 调用原来列表中的元素与 arr2 中的元素进行比较,而向 ans

中插入 arr2 的数,就可以有效避免这个问题。

算法2:全排列列表

给定一个数字列表,返回其所以的可能列表

# 问题示例

# 输入[1],输出[[1]],输入[1,2,3],输出[[1,2,3,],[1,3,2],[2,1,3],[2,3,1],[3,1,2],[3,2,1]]。

# 代码实现class Solution:# 参数nums:整数数组# 返回值:排列后的列表def arrange(self, nums):def _arrange(result, temp, nums):if nums == []:result += [temp]else:for i in range(len(nums)):_arrange(result, temp + [nums[i]], nums[:i] + nums[i + 1:])if nums is None:return []if nums is []:return [[]]result = []_arrange(result, [], sorted(nums))return result# 主函数

if __name__ == '__main__':s = Solution()nums = [1, 2, 3]result = s.arrange(nums)print("输入:", nums)print("输出:", result)