专门做电商的招聘网站做网站赚钱还是做app赚钱

1.进入若依官网,找到我们要下的微服务版框架

2.点击进入gitee,获取源码,下载到本地

3.下载到本地后,用Idea打开,点击若依官网,找到在线文档,找到微服务版本的,当然你不看文档,直接按我说的做也OK啦!

4.点开环境部署,跟着一步步的操作就好(就是接下来图片里的的步骤),第5步可以放到安装Nacos后再进行。

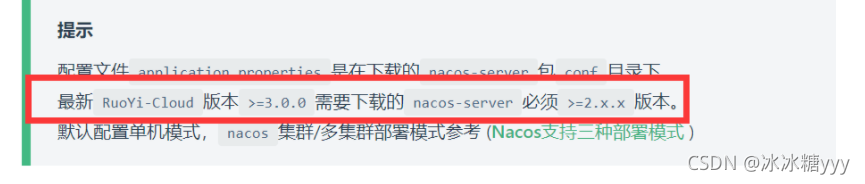

5.我当时就没看到这一行,Nacos要下2.X.X版本的,找了好久的错误!!!

6.下面我们来说一下nacos的安装,第一步当然是打开Nacos官网了

6.下面我们来说一下nacos的安装,第一步当然是打开Nacos官网了

7.点击v2.0.3,因为下载最新的若依框架,客户端那边的Nacos是2.0.x版本的,所以我们服务端的Nacos也要下载2.0.x版本的,否则会报错!

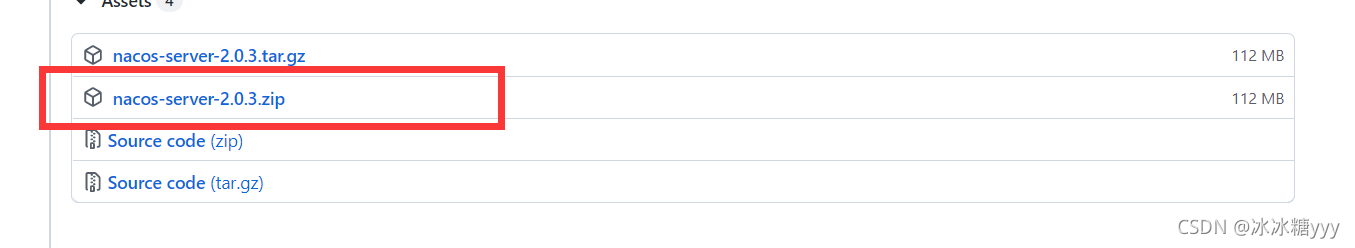

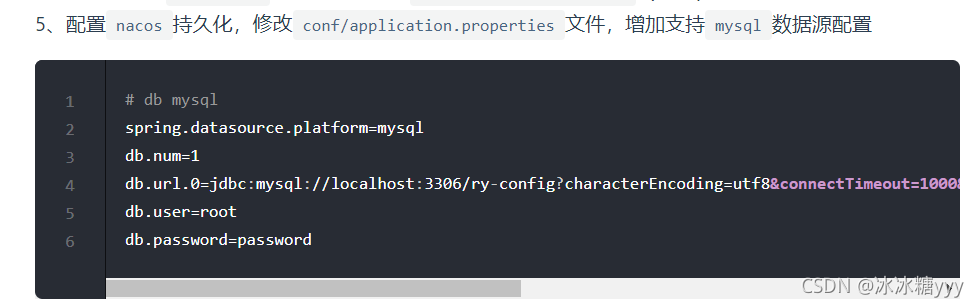

8.点击第二个下载到本地,然后解压,先进行我们之前没有改完的配置,修改成自己的数据库用户名和密码。

8.点击第二个下载到本地,然后解压,先进行我们之前没有改完的配置,修改成自己的数据库用户名和密码。

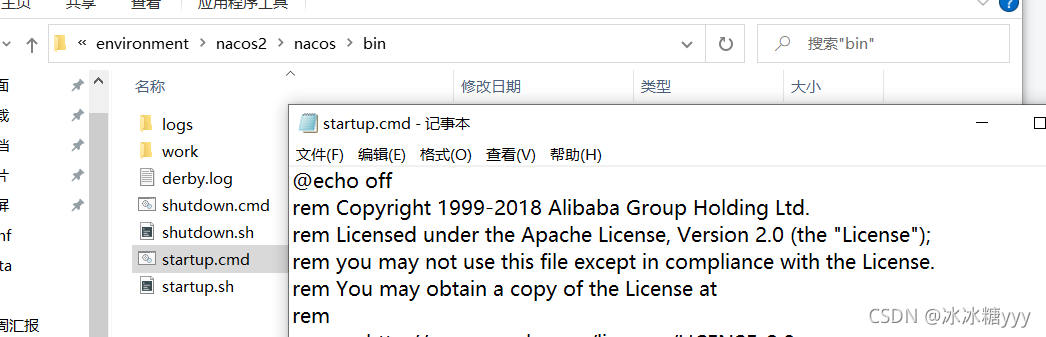

9.进入如下目录,对startup.cmd进行修改,把mode里的内容改成standalone,即启动方式为standalone(单机版)。

9.进入如下目录,对startup.cmd进行修改,把mode里的内容改成standalone,即启动方式为standalone(单机版)。

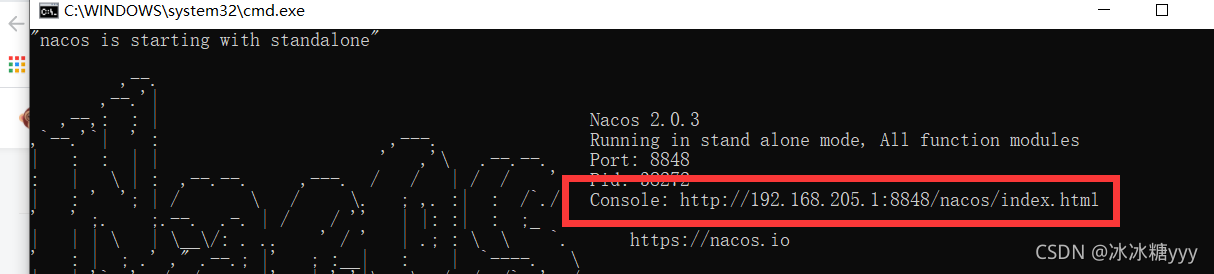

10.这是点击该文件启动Nacos,弹出下面这个窗口,且没有报错,就是启动成功!

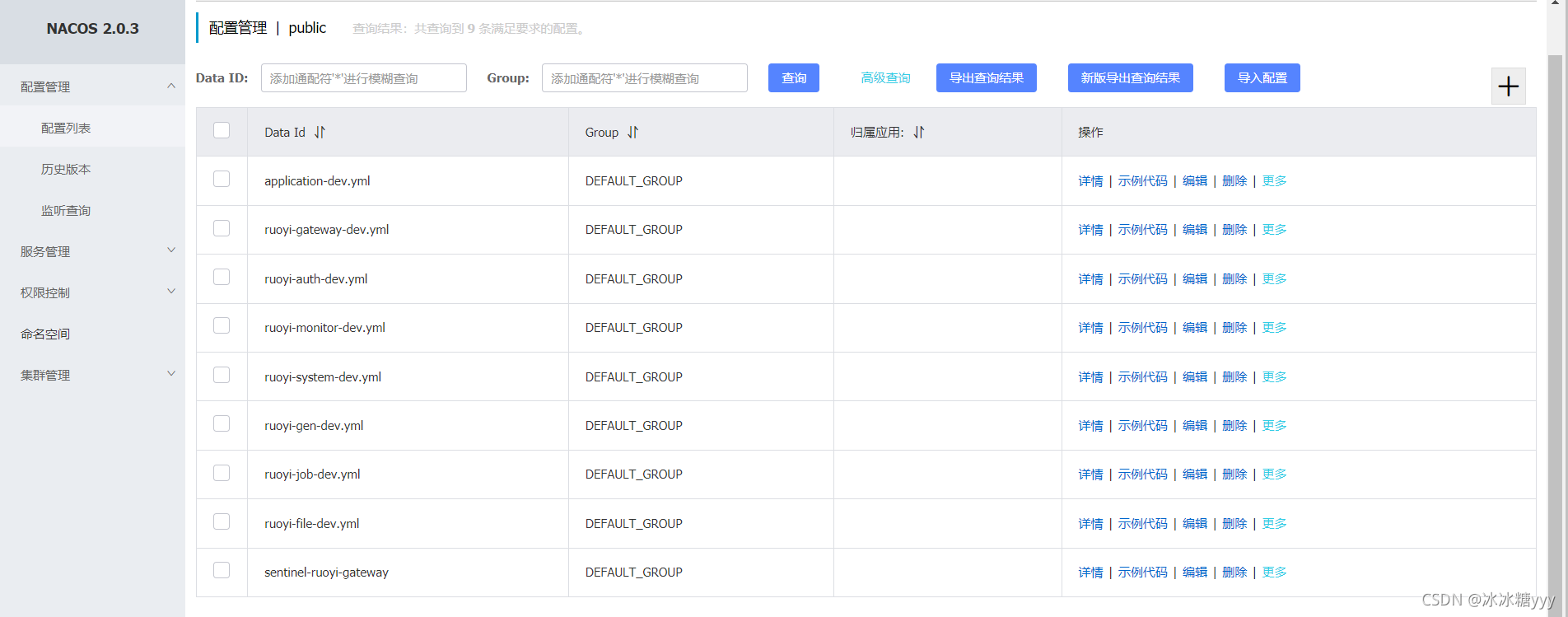

11.这时候我们输入网址,出现Nacos登录页面,用户名和密码都是nacos,进入后,有这样一个页面,我们点编辑进行对应的修改(主要是修改里面的数据库密码)。

11.这时候我们输入网址,出现Nacos登录页面,用户名和密码都是nacos,进入后,有这样一个页面,我们点编辑进行对应的修改(主要是修改里面的数据库密码)。

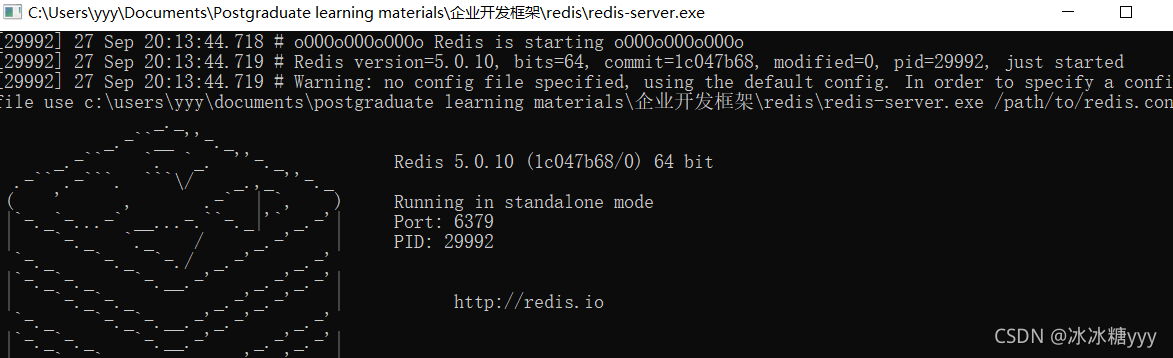

12.修改完成后,我们启动redis。

这里附上redis的菜鸟教程,下载,启动都有 链接:Redis 安装 | 菜鸟教程

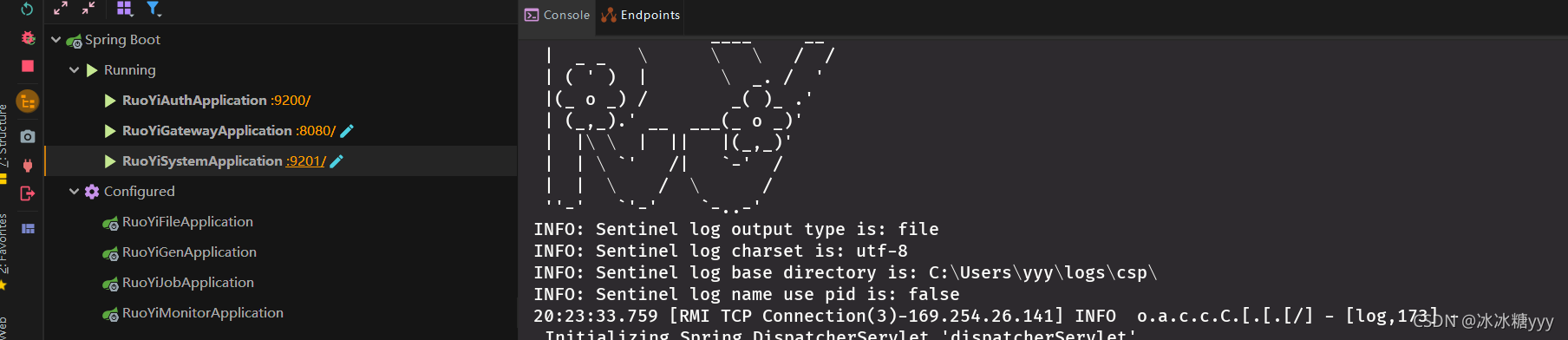

13.然后进入若依框架启动后端

14.后端启动成功!!!

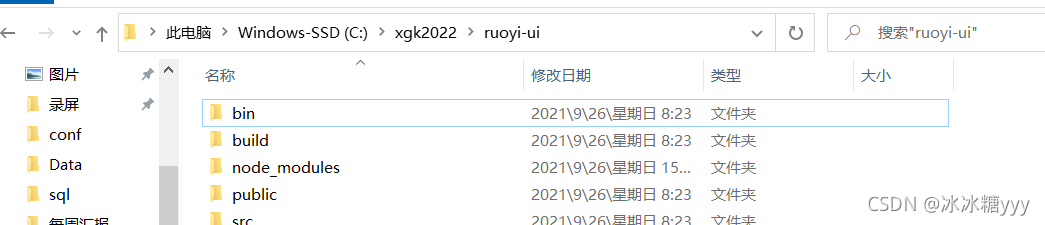

15.我们下面来启动前端

把整个项目的ruoyi-ui这个包单独拖出来,进入目录,点击地址栏输入cmd,进入终端模式,安装依赖 ,使用这个命令:npm install -g mirror-config-china --registry=http://registry.npm.taobao.org

(能够使用这个给命令的前提在于已安装Note.js,下载地址Node.js,下载第一个维护版的)

16.然后输入npm run dev,启动框架前端

17.启动成功后,弹出这样一个页面,输入验证码登陆进去,说明我们部署完成!

18.进入若依首页,可以开始开发之旅啦!

18.进入若依首页,可以开始开发之旅啦!