福建省建设相关网站一个空间放多个网站

描述

分两次从控制台接收用户的两个输入:第一个内容为“人名”,第一个内容为“心里

话”。

然后将这两个输入内容组成如下句型并输出出来:

1.(人名),I want to say,(心里话

2.

输入输出示例:

输入:Kim

You are beautiful!

输出:

Kim,I want to say,You are beautiful!

(答案在文末,有两种答案)

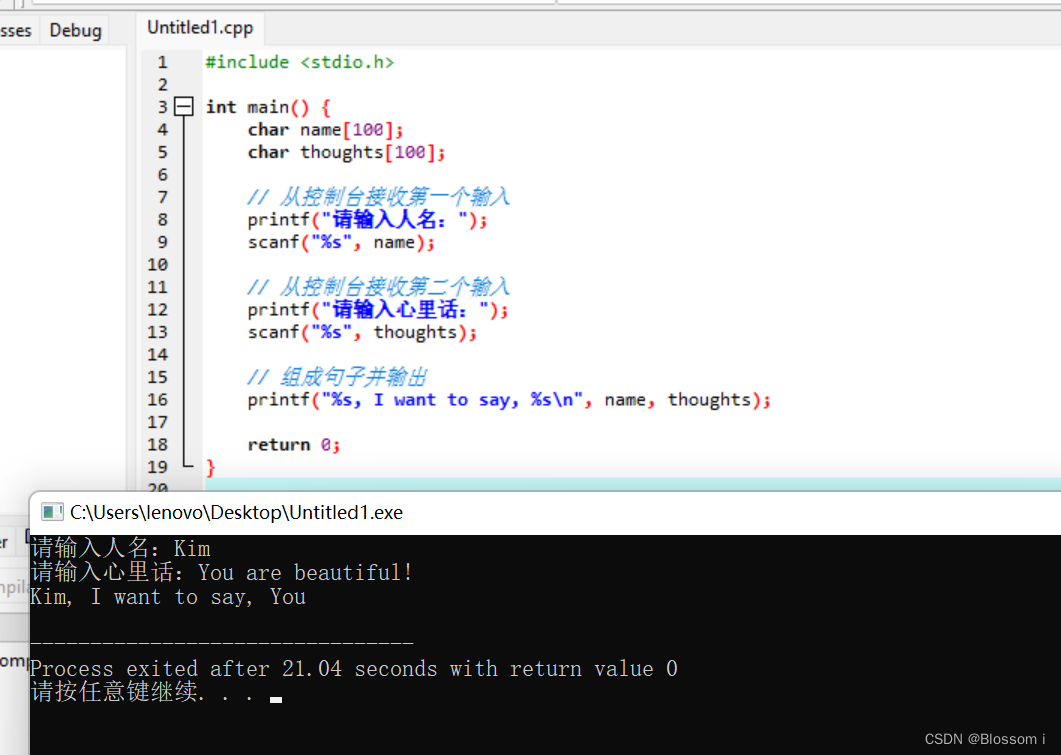

错误演示:

#include <stdio.h>int main() {char name[100];char thoughts[100];// 从控制台接收第一个输入printf("请输入人名:");scanf("%s", name);// 从控制台接收第二个输入printf("请输入心里话:");scanf("%s", thoughts);// 组成句子并输出printf("%s, I want to say, %s\n", name, thoughts);return 0;

}

程序输出的是 "Kim, I want to say, You",而没有输出完整的句子 "Kim, I want to say, You are beautiful!",可能是因为输入的心里话太长,超出了 scanf 函数读取字符串的默认长度。此时可以使用指定最大长度的方式来接收输入。

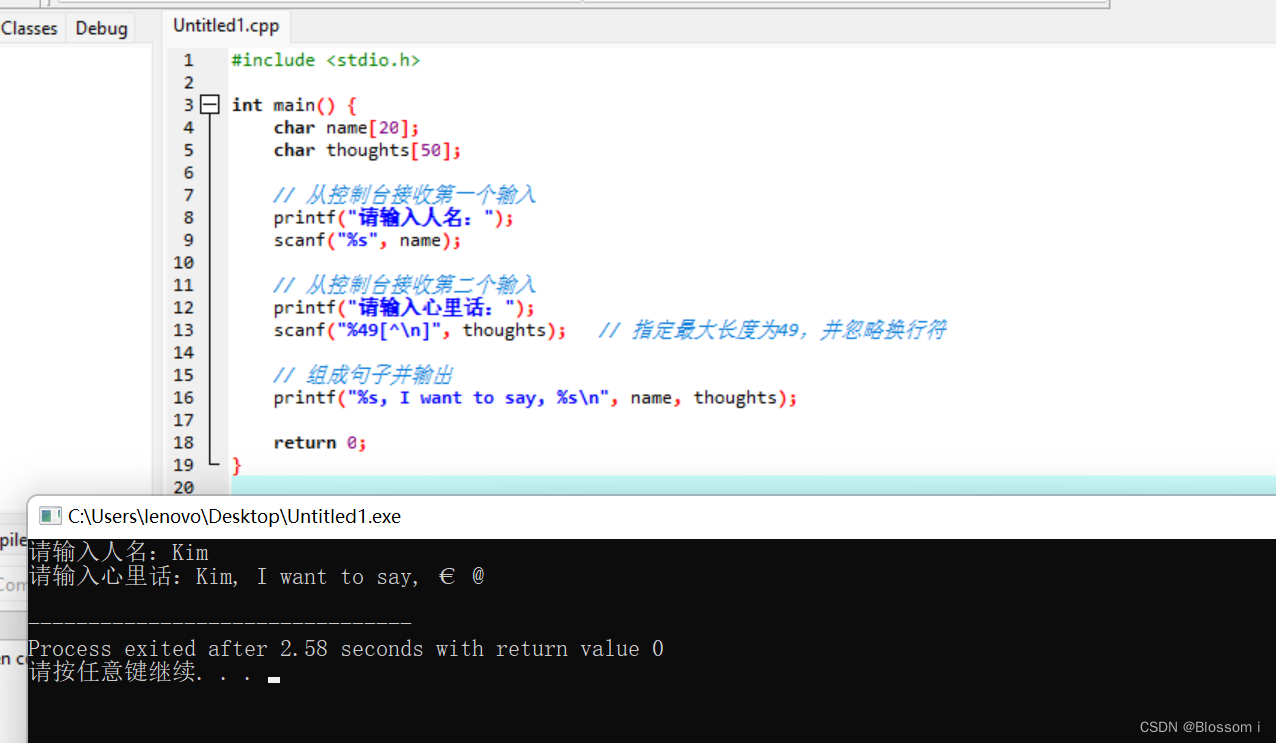

修改 C 语言代码如下:

#include <stdio.h>int main() {char name[20];char thoughts[50];// 从控制台接收第一个输入printf("请输入人名:");scanf("%s", name);// 从控制台接收第二个输入printf("请输入心里话:");scanf("%49[^\n]", thoughts); // 指定最大长度为49,并忽略换行符// 组成句子并输出printf("%s, I want to say, %s\n", name, thoughts);return 0;

}

如果在输入心里话时出现 "Kim, I want to say, € @报错" 这样的输出,那么很可能是在输入时发生了中文编码问题。可以尝试以下方法解决:

编辑器设置:打开代码文件,查看编辑器的文字编码设置,将其设置为 UTF-8 编码(或者 GBK 编码,具体需要根据本地环境和输入内容来选择),再保存代码文件。

输出调试:在 C 语言程序中加入一些输出语句,以便查看程序的执行情况,比如:

printf("输入的心里话是:%s\n", thoughts); // 输出调试信息

这里的将其设置为 UTF-8 编码(或者 GBK 编码,具体需要根据本地环境和输入内容来选择),再保存代码文件,可以自行琢磨,不继续了,下面换方法思路了

方法一:使用 fgets 函数来接收用户输入

所以最终改出来的代码为:

#include <stdio.h>

#include <string.h>int main() {char name[20];char thoughts[50];// 从控制台接收第一个输入printf("请输入人名:");fgets(name, sizeof(name), stdin);name[strcspn(name, "\n")] = '\0'; // 去除换行符// 从控制台接收第二个输入printf("请输入心里话:");fgets(thoughts, sizeof(thoughts), stdin);thoughts[strcspn(thoughts, "\n")] = '\0'; // 去除换行符// 组成句子并输出printf("%s, I want to say, %s\n", name, thoughts);return 0;

}

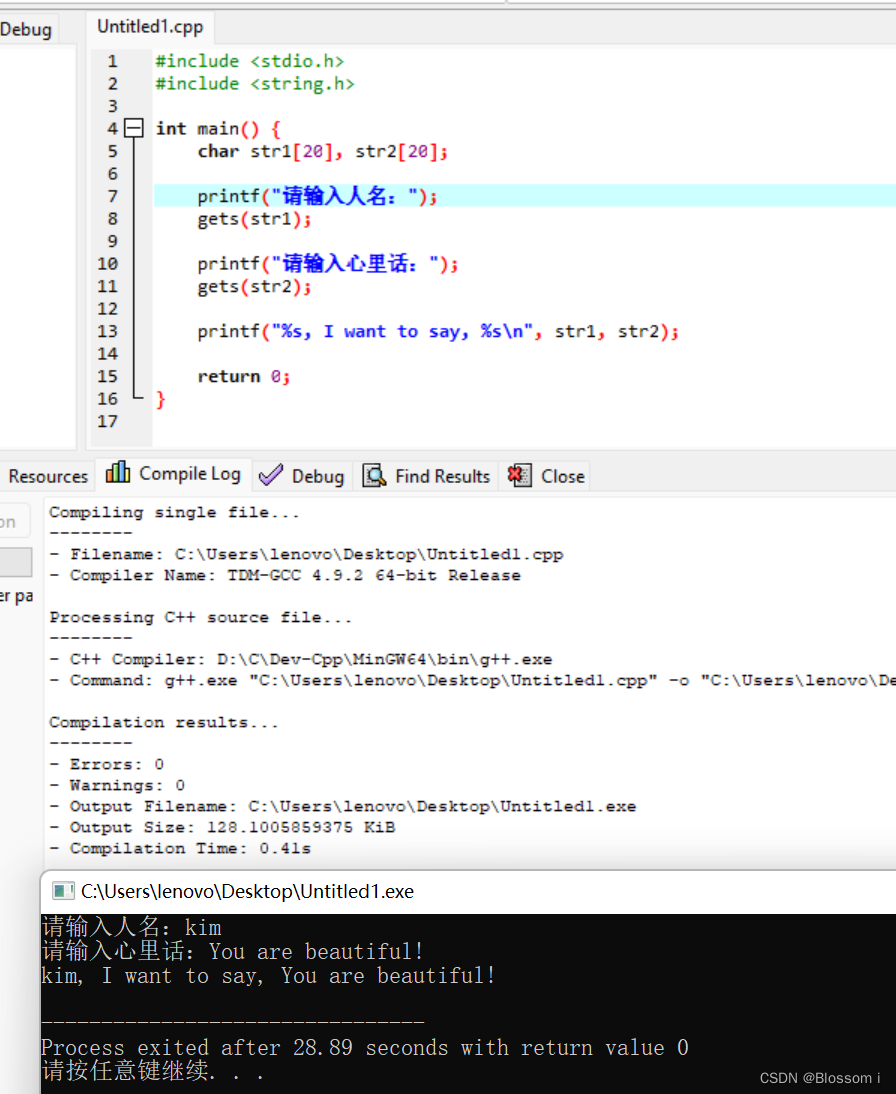

方法二:使用 gets 函数

#include <stdio.h>

#include <string.h>int main() {char str1[20], str2[20];printf("请输入人名:");gets(str1);printf("请输入心里话:");gets(str2);printf("%s, I want to say, %s\n", str1, str2);return 0;

}

使用 gets 函数来读取输入。gets 函数在读取一行输入时不会将换行符作为输入的一部分,因此不需要去除换行符。接下来,使用 printf 函数输出组合好的字符串。

虽然 gets 函数比 fgets 函数用起来更方便,但由于 gets 函数不能限制输入的长度,容易发生缓冲区溢出,造成系统安全漏洞,所以在实际开发中建议使用 fgets 函数,并在读取用户输入前检查输入字符的长度。