公司网站建设的意义方案dedecms 网站地图模板

各位CSDN的uu们好呀,终于到小雅兰的STL的学习了,下面,让我们进入C++STL的世界吧!!!

1. 什么是STL

2. STL的版本

3. STL的六大组件

4. STL的重要性

5. 如何学习STL

6.STL的缺陷

7.为什么要学习string类

8.标准库中的string类

什么是STL

STL(standard template libaray-标准模板库):是C++标准库的重要组成部分,不仅是一个可复用的组件库,而且是一个包罗数据结构与算法的软件框架。

STL的版本

- 原始版本:Alexander Stepanov、Meng Lee 在惠普实验室完成的原始版本,本着开源精神,他们声明允许任何人任意运用、拷贝、修改、传播、商业使用这些代码,无需付费。唯一的条件就是也需要向原始版本一样做开源使用。 HP 版本--所有STL实现版本的始祖。

- P. J. 版本:由P. J. Plauger开发,继承自HP版本,被Windows Visual C++采用,不能公开或修改,缺陷:可读性比较低, 符号命名比较怪异。

- RW版本:由Rouge Wage公司开发,继承自HP版本,被C+ + Builder 采用,不能公开或修改,可读性一般。

- SGI版本:由Silicon Graphics Computer Systems,Inc公司开发,继承自HP版本。被GCC(Linux)采用,可移植性好, 可公开、修改甚至贩卖,从命名风格和编程 风格上看,阅读性非常高。我们后面学习STL要阅读部分源代码, 主要参考的就是这个版本。

STL的六大组件

STL的重要性

STL模板分为容器、迭代器、算法和函数对象四个部分。

容器是一种数据结构,它可以存储一组数据并提供对这些数据的访问方式。STL中提供了多种容器,包括序列容器(如vector、list、deque)、关联容器(如set、map)等等。每种容器都提供了不同的操作方法,可以满足不同的需求。

迭代器是一种抽象的概念,它提供了对容器中元素的遍历和访问方式。STL中提供了多种迭代器,包括随机访问迭代器、双向迭代器、前向迭代器等等。不同类型的迭代器支持不同的操作方式,可以在不同的场景下使用。

算法是STL中的重要部分,它提供了多种常见的算法实现,如排序、查找、遍历等。这些算法可以应用于不同类型的容器和迭代器上,使得程序开发变得更加简单和高效。

函数对象是一种可以被调用的对象,它可以像函数一样被调用。STL中提供了多种函数对象,包括算术运算、关系运算、逻辑运算等等。函数对象可以和STL中的算法一起使用,使得算法更加灵活和通用。

总的来说,STL模板提供了丰富的工具集合,可以帮助程序员更加高效地开发C++程序。使用STL模板可以避免一些繁琐的工作,如内存管理、数据结构实现等等,从而使程序员能够更加关注于问题的本质,提高代码的可读性和可维护性。

在笔试中

把二叉树打印成多行_牛客题霸_牛客网

重建二叉树_牛客题霸_牛客网

用两个栈实现队列_牛客题霸_牛客网

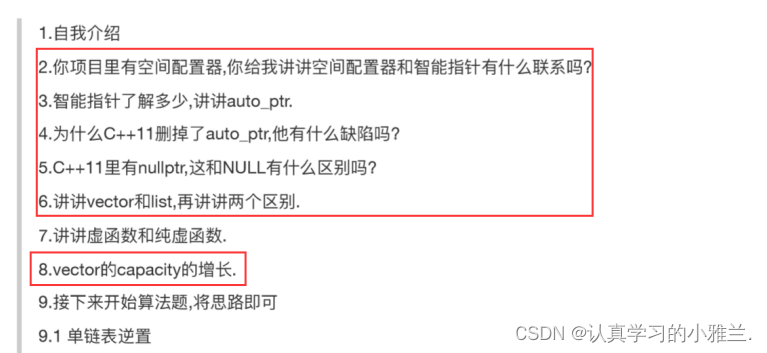

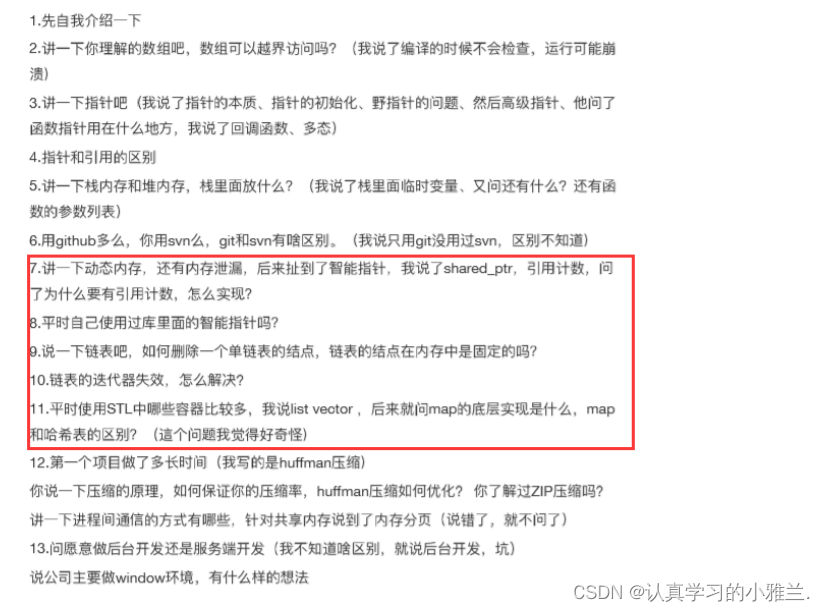

在面试中

在工作中

网上有句话说:“不懂STL,不要说你会C++”。STL是C++中的优秀作品,有了它的陪伴,许多底层的数据结构以及算法都不需要自己重新造轮子,站在前人的肩膀上,健步如飞的快速开发。

如何学习STL

简单总结一下:学习STL的三个境界:能用,明理,能扩展 !!!

STL的缺陷

- STL库的更新太慢了。这个得严重吐槽,上一版靠谱是C++98,中间的C++03基本一些修订。C++11出 来已经相隔了13年,STL才进一步更新。

- STL现在都没有支持线程安全。并发环境下需要我们自己加锁。且锁的粒度是比较大的。

- STL极度的追求效率,导致内部比较复杂。比如类型萃取,迭代器萃取。

- STL的使用会有代码膨胀的问题,比如使用vector/vector/vector这样会生成多份代码,当然这是模板语法本身导致的。

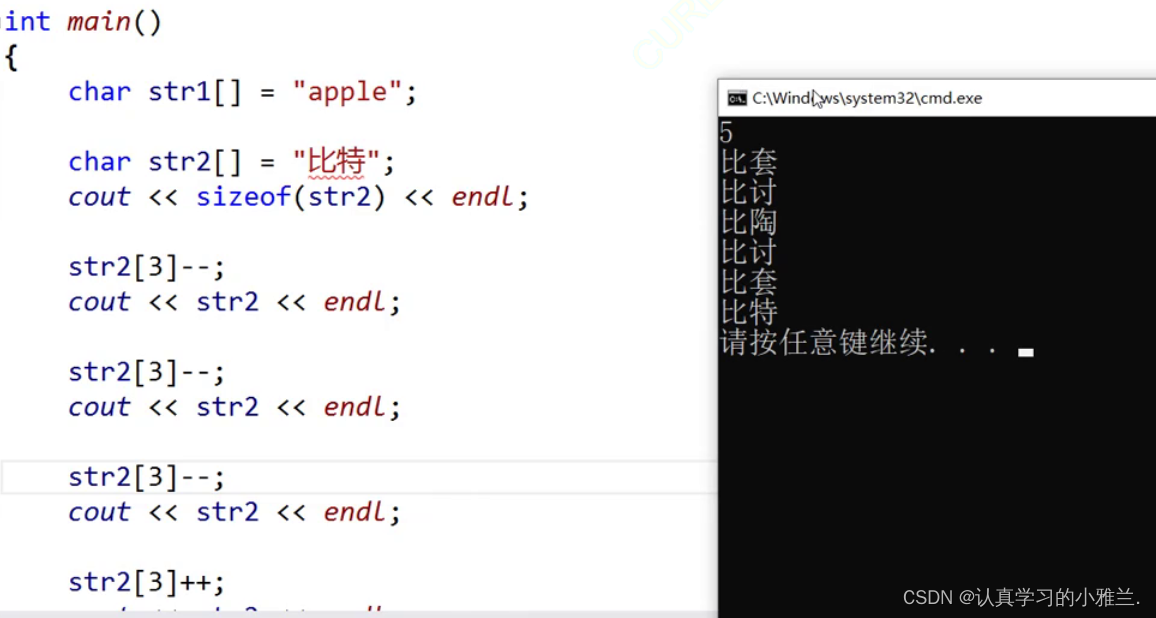

为什么学习string类?

C语言中的字符串

C语言中,字符串是以'\0'结尾的一些字符的集合,为了操作方便,C标准库中提供了一些str系列的库函数, 但是这些库函数与字符串是分离开的,不太符合OOP的思想,而且底层空间需要用户自己管理,稍不留神可能还会越界访问。

两个面试题

把字符串转换成整数_牛客题霸_牛客网

力扣(LeetCode)官网 - 全球极客挚爱的技术成长平台

在OJ中,有关字符串的题目基本以string类的形式出现,而且在常规工作中,为了简单、方便、快捷,基本 都使用string类,很少有人去使用C库中的字符串操作函数。

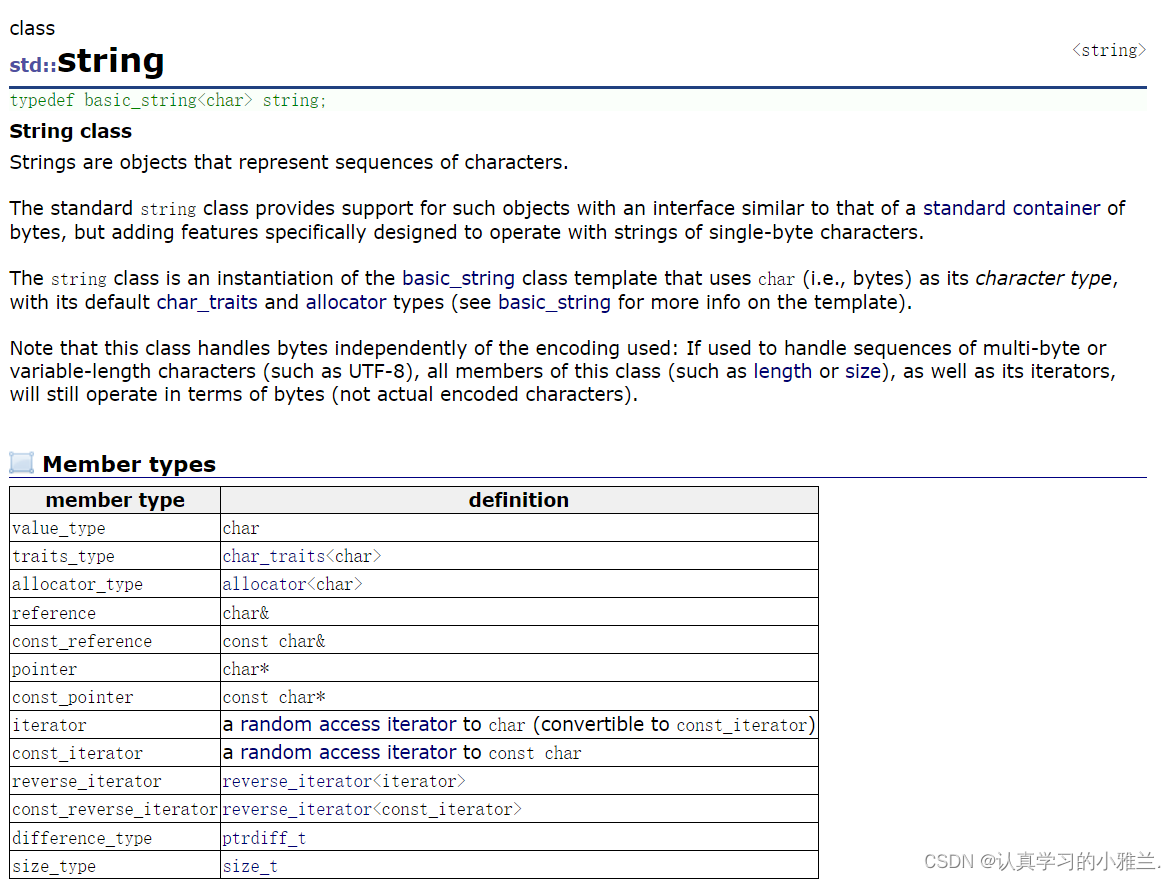

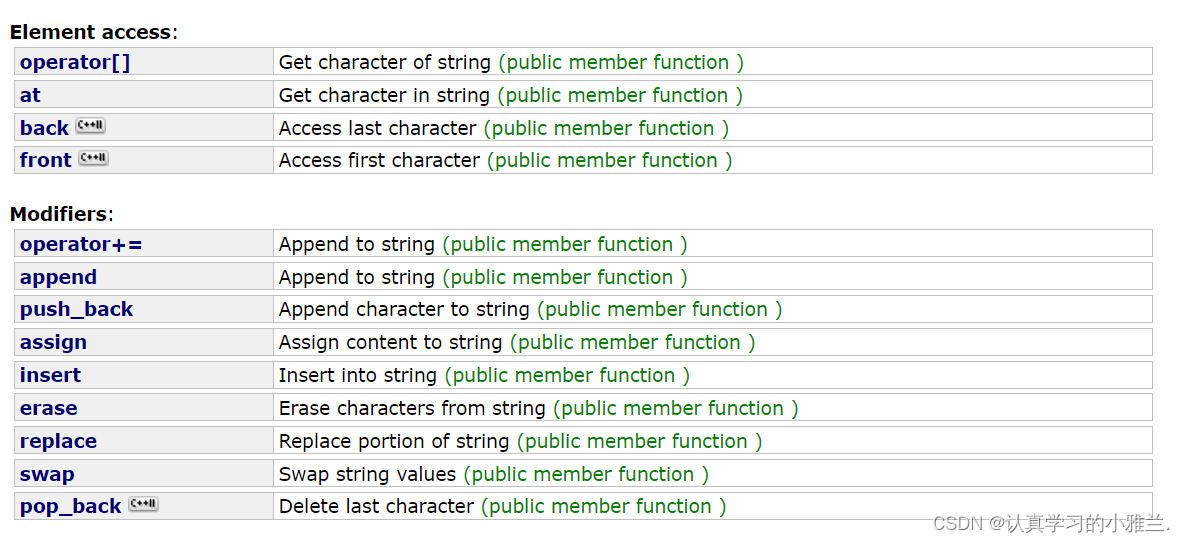

标准库中的string类

string类(了解)

string - C++ Reference

百度百科-验证

百度百科-验证

- 字符串是表示字符序列的类

- 标准的字符串类提供了对此类对象的支持,其接口类似于标准字符容器的接口,但添加了专门用于操作 单字节字符字符串的设计特性。

- string类是使用char(即作为它的字符类型,使用它的默认char_traits和分配器类型(关于模板的更多信 息,请参阅basic_string)。

- string类是basic_string模板类的一个实例,它使用char来实例化basic_string模板类,并用char_traits和allocator作为basic_string的默认参数(根于更多的模板信息请参考basic_string)。

- 注意,这个类独立于所使用的编码来处理字节:如果用来处理多字节或变长字符(如UTF-8)的序列,这个 类的所有成员(如长度或大小)以及它的迭代器,将仍然按照字节(而不是实际编码的字符)来操作。

总结:

- string是表示字符串的字符串类

- 该类的接口与常规容器的接口基本相同,再添加了一些专门用来操作string的常规操作。

- string在底层实际是:basic_string模板类的别名,typedef basic_string string;

- 不能操作多字节或者变长字符的序列。

在使用string类时,必须包含#include头文件以及using namespace std;

好啦,剩下的string的详细内容小雅兰下一篇博客再来介绍,敬请期待吧!!!