网站模板 免费下载做网站页面视频教学

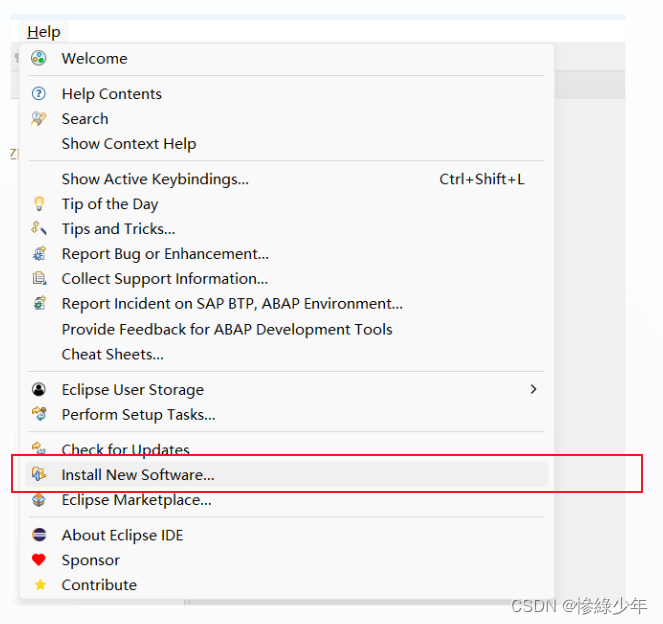

- Eclipse->Help->Install New software

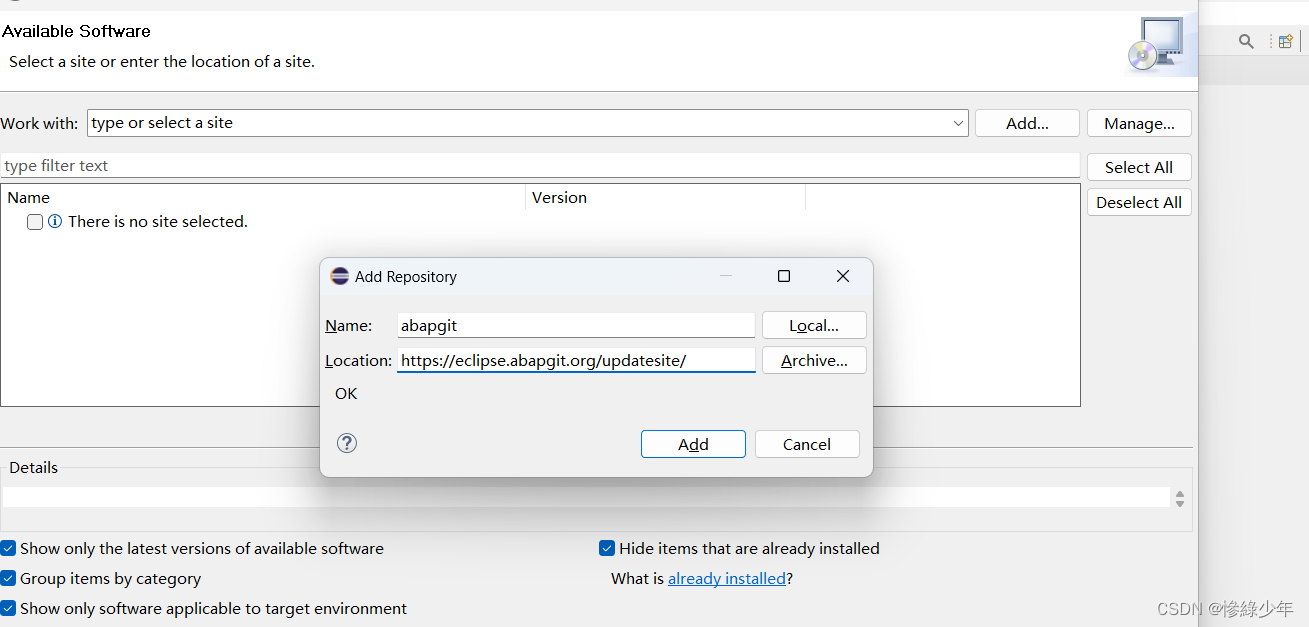

- 添加地址

https://eclipse.abapgit.org/updatesite/

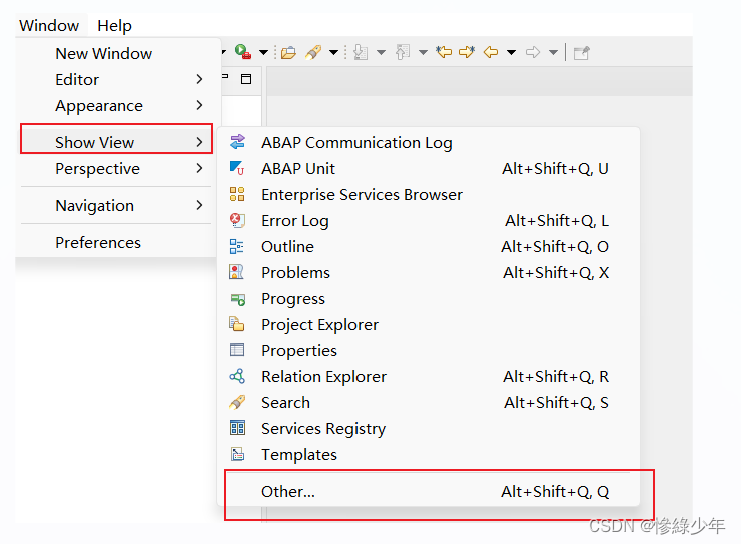

安装完成打开

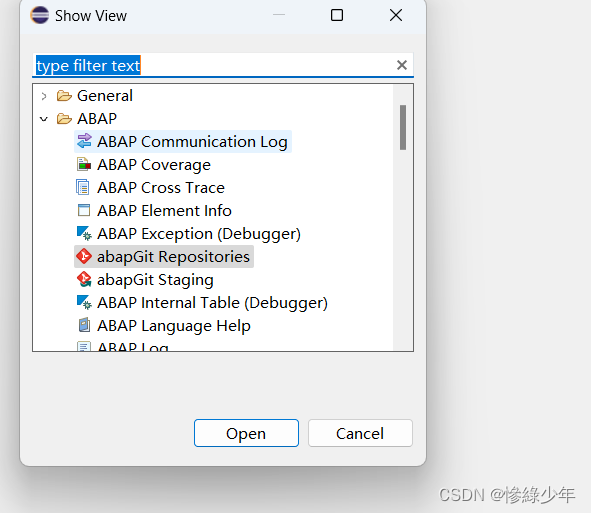

选择abapGit repositories,先添加仓库

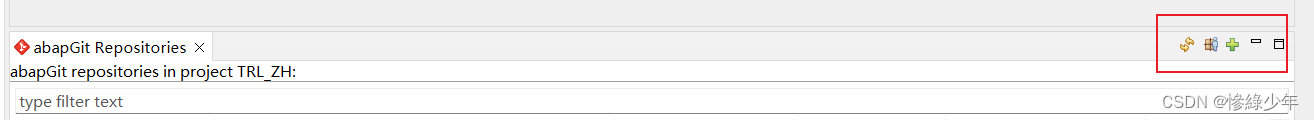

点下图+添加自己仓库

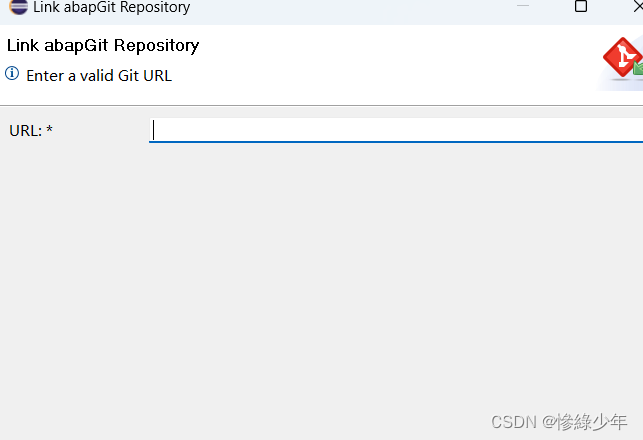

如图添加仓库地址

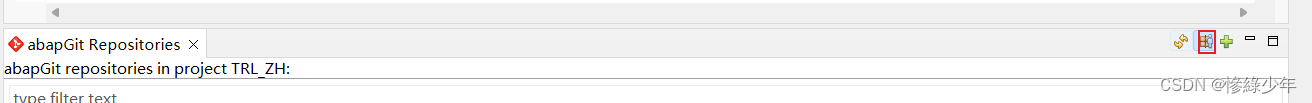

添加完仓库后,点击我的仓库

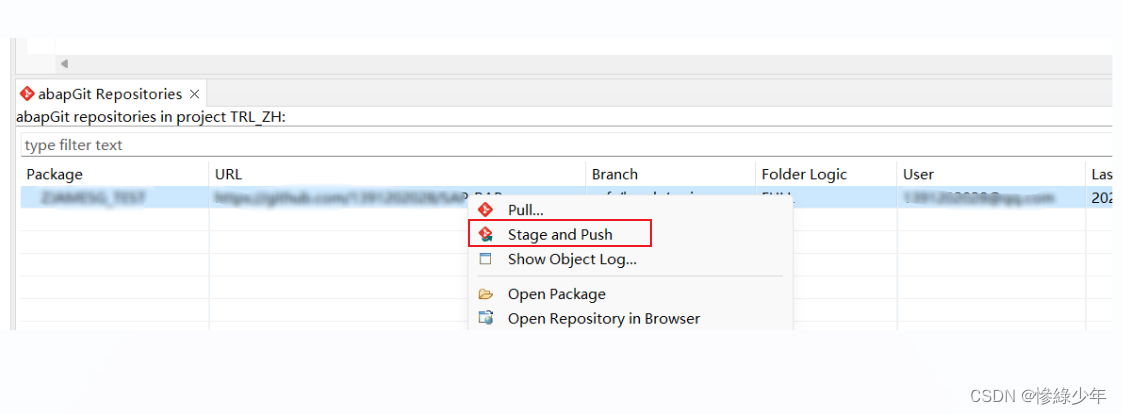

右键选中行,可以进行push和pull

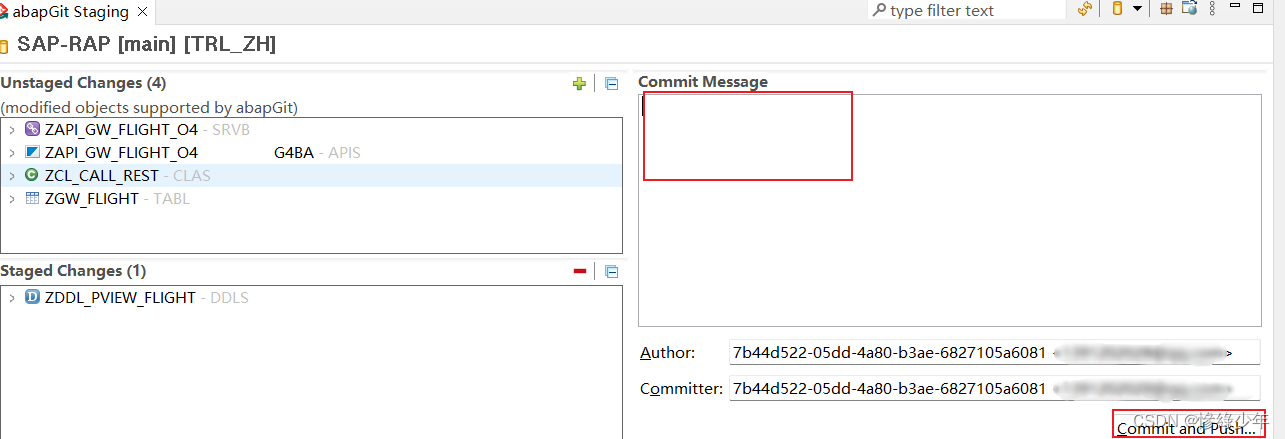

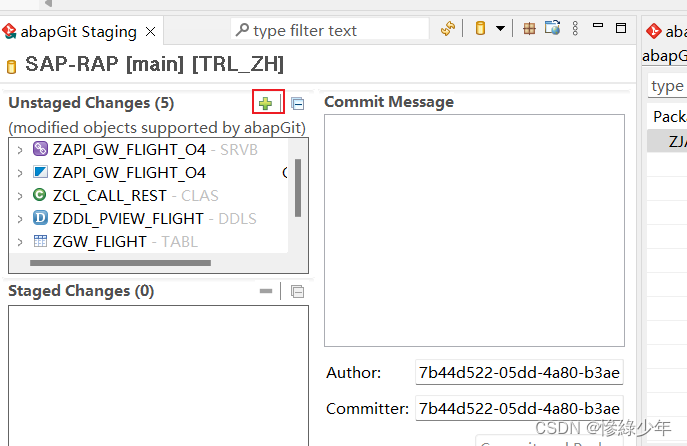

可以点下面加号(也可以直接拖下去),将程序添加至Staged Changes

输入Commit Message 即可点击commit and push