有赞分销seo外推软件

基于新手小白,使用Labview实现99乘法表,敢于发表自己的一点方法,还请各位大侠放过!

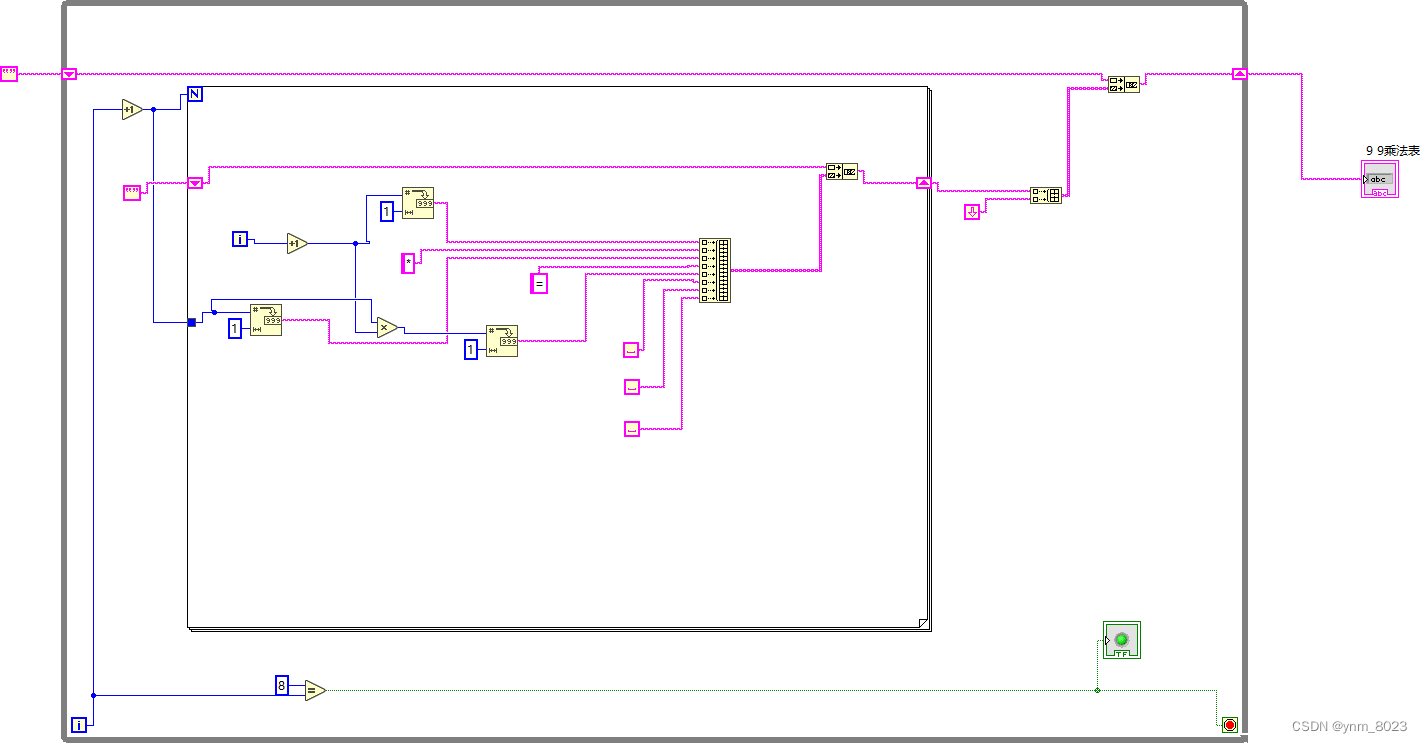

如下:

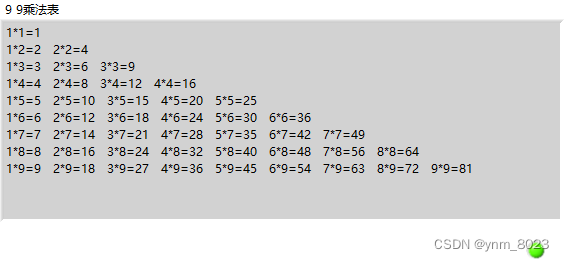

运行效果如下:

思路为:将要显示出来的数据,全部转换为字符串形式,再塞入到数组中,拼接字符串,在整个打印出来;

外部使用的While循环,内部嵌套for循环,While循环显示第一位乘数,for循环显示第二位乘数。

虽然方法笨了点,但也是新手小白自己按思路一点一点拼接而成,各位大神请指教!

基于新手小白,使用Labview实现99乘法表,敢于发表自己的一点方法,还请各位大侠放过!

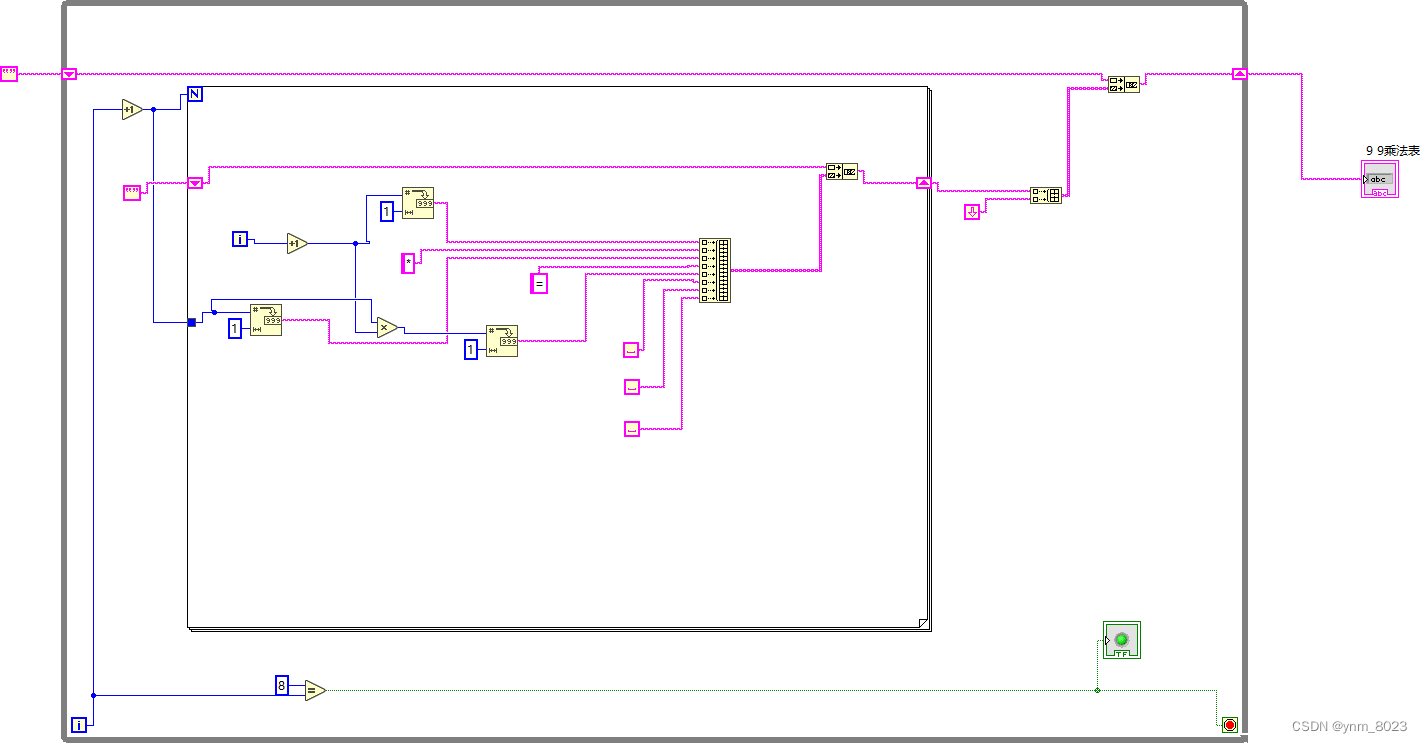

如下:

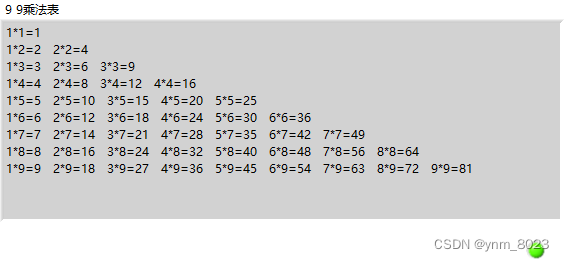

运行效果如下:

思路为:将要显示出来的数据,全部转换为字符串形式,再塞入到数组中,拼接字符串,在整个打印出来;

外部使用的While循环,内部嵌套for循环,While循环显示第一位乘数,for循环显示第二位乘数。

虽然方法笨了点,但也是新手小白自己按思路一点一点拼接而成,各位大神请指教!