商城网站建设信息网站建设开发价格怎么算

可以通过更改角度精度的方式把角度的标注精确到小数点后几位,具体方法如下:

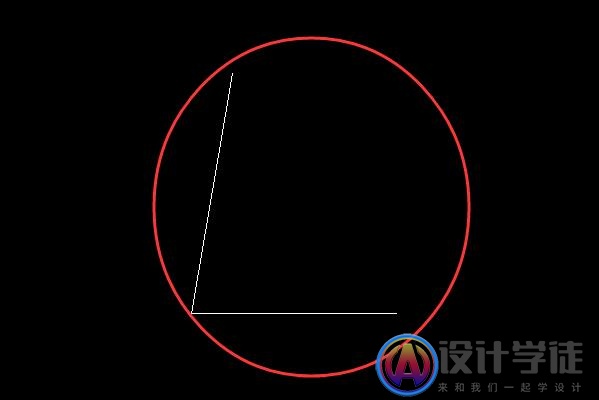

1、打开一个CAD文档,在文档中画一个角,如下图:

文章源自设计学徒自学网-https://www.sx1c.com/47920.html

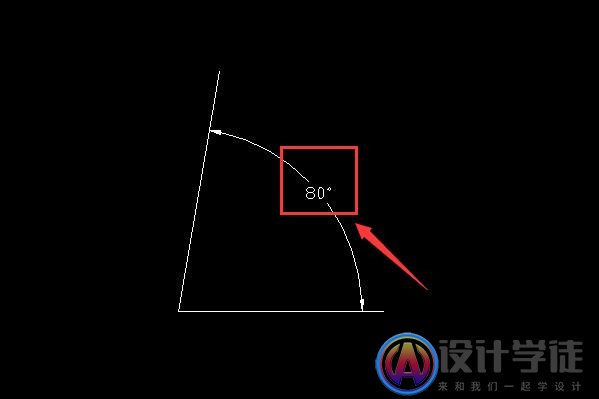

2、给此角进行角度的标注,此时标注显示为“80°”:

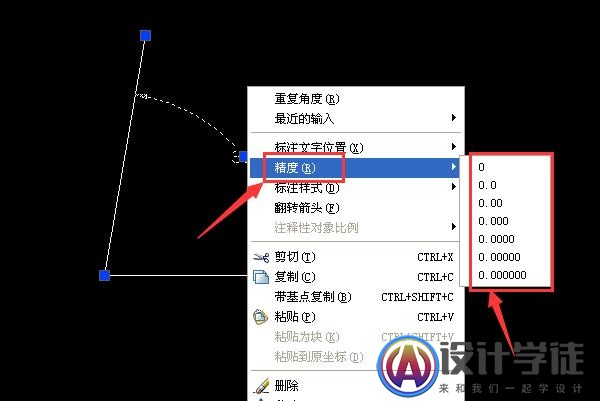

3、鼠标左键单击选中此标注,然后单击右键,在打开的列表中找到“精度”,后面会列出不同的精度可以选择,选择其中的“0.000”:

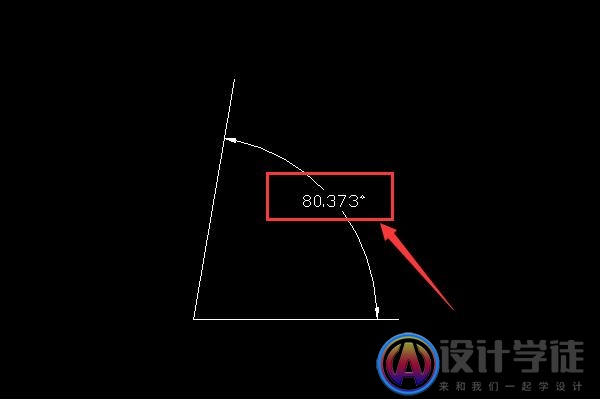

4、此时再看角度的标注,已经由80°变成了80.373°,这样就实现了角度标注精度的变更:

推荐:dbf转成excel怎么操作? | https://www.sx1c.com/47926.html