网站头部怎么做百度用户服务中心电话

文章目录

- 前言

- 开发环境

- 续订会员资格

- 转让账户持有人

- 验证身份

- 1. 实名认证

- 2. 联系信息

- 更换订阅的账号

- 最后

前言

公司有一个开发者账号快到期了需要续订会员资格,刚注册时是用我自己的个人账号完成的订阅购买。现在想来有点不妥,于是尝试更换用于订阅的账号,发现找不到入口。折腾了一番成功完成了更换,在这记录一下以备不时之需。

开发环境

- iOS: 16.6

- Apple Developer App: 10.4.1

续订会员资格

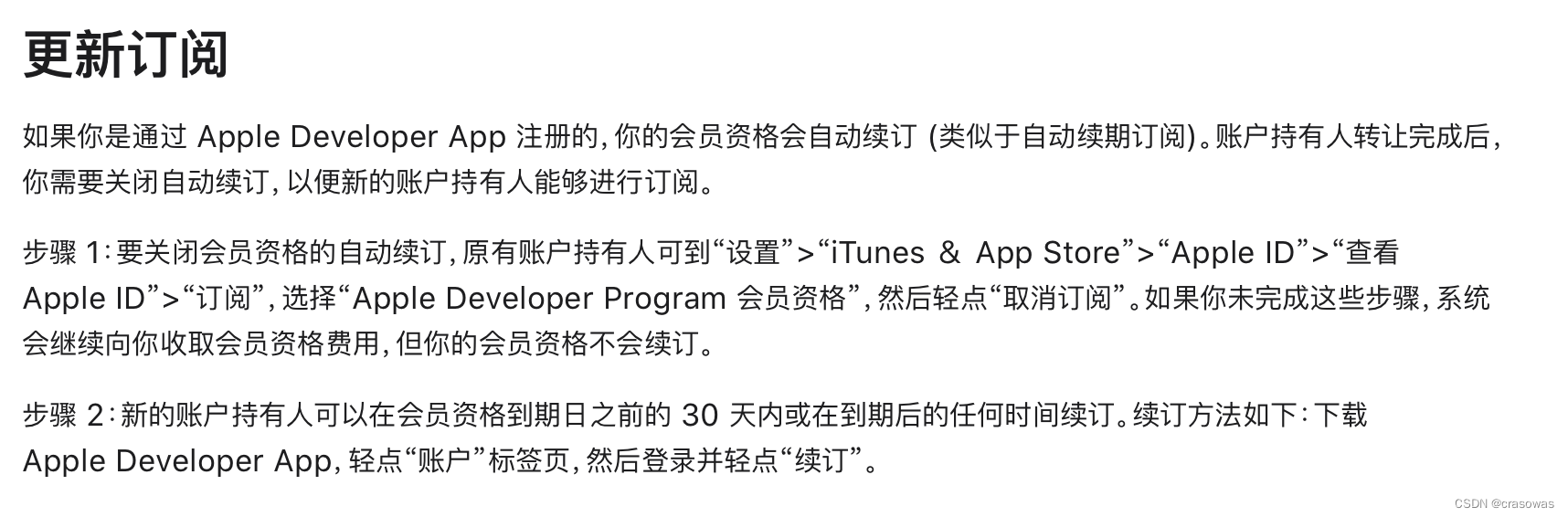

大概从2021年开始,注册开发者账号需要在Apple Developer App上完成,这种方式注册的开发者账号只能通过订阅的方式购买或续订会员资格。

续订入口位于iPhone(或iPad)上的[设置] -> [顶部 Apple ID] -> [订阅],订阅项目如下图所示:

因为我打算更换订阅账号,所以已经取消了自动订阅。通常这个订阅项目只在首次订阅购买的账号中有,举个例子🌰:A账号是公司用于注册开发者的账号(登录Apple Developer App),B账号是个人的账号(登录iPhone),在iPhone上注册A账号时订阅购买用的账号是本机登录的B账号,那么后续续订入口只能在B账号中看到。

对于更早之前通过网页注册的,实测还可以在开发者网站找到续订入口,通过双标(或者叫双币)信用卡完成续订。

我无法理解为什么不能让开发者自由选择续订方式,对于个人开发者而言,新的订阅方式确实方便了很多,能通过支付宝/微信等订阅,但是对于公司开发者而言,新的订阅方式并没有方便多少,而且还会因为是内购购买导致没办法开发票(报销麻烦😣)。

参考文档:

- 计划续订

转让账户持有人

通过联系苹果客服得知,目前只能通过转让账户持有人的方式更换订阅账号。转让账户持有人的官方支持文档确实有提及这方面的内容:

按文档描述,我们需要先将账户持有人转让给其他人(账号),然后快到期或已过期时就可以在Apple Developer App登录新的账户持有人账户后看到续订入口。

补充一点,转让账户持有人不会改变法人实体等信息,而且可以随时取消转让或转回原有账户持有人。转让成功后,原账户持有人还会以管理员的身份留在团队中。如果需要更改App所属的公司,可以通过转让App功能完成。

已有的账户持有人(公司的开发者账号)一般都是专用的不能更改,所以计划先转给某个公司核心人员(比如boss,后续订阅由他的个人账号完成),订阅成功后再将账户持有人转回去,最终账户持有人不变,用于订阅的账号也完成了切换。

登录开发者网站,找到[会员资格详细信息] -> [更新你的信息] -> [转让账户持有人职能] -> [选择一位候选人],如果受让人列表没找到转让目标用户,请先在用户与访问中邀请对方加入团队。

提交转让申请后,对方登录开发者网站会看到这个:

这时大概率会因为账号没有验证身份而无法接受请求,需要前往Apple Developer App验证身份。

验证身份

验证身份是注册开发者账号必须要完成的步骤,需要接受转让请求的账号登录Apple Developer App(如果没安装,请前往AppStore安装),找到[账户] -> [验证您的身份]开始验证身份。

注意,验证身份前请检查以下条件是否满足(如果都满足后面还是有问题建议尝试更换设备):

参考文档:

- 使用 Apple Developer App 注册和验证你的身份

验证身份分两步:

1. 实名认证

如实填写实名信息和拍摄自拍照很容易完成这一步。关于下图中的提示,实测同一个人的身份可以验证不止一个Apple ID:

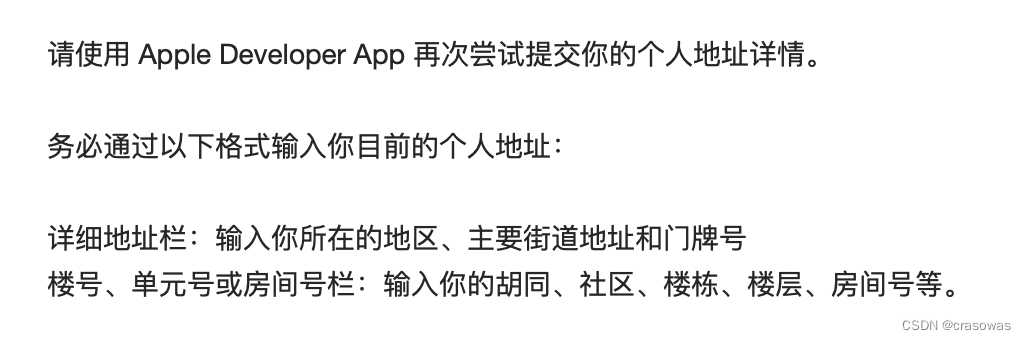

2. 联系信息

- 姓氏/名字:填姓和名的拼音,首字母大小写都可以

- 地址行 1:参照这个格式

xx区/县xx街道/路xx号填写,请不要填多了,不是越详细越好,多了识别不了会被判为无效地址。需要特别注意很多完整地址同时包含xx街道和xx路,请只选其中一个填写 - 地址行 2:参照这个格式

xx小区xx号楼填写,同上请不要填多了,不过实测加上房间号也是可以的 - 市/镇:填所在城市名称,例如

xx市 - 州/省:选择所在的省份

- 邮政编码:填所在区县的邮政编码即可(感觉没检查)

注意,以上所填地址为个人地址,请不要填公司地址。

如果出现了弹框提示[请输入一个有效的地址]:

请认真检查地址行是否已经按照格式填写。

如果你已经多次提交失败,点击提交会直接关闭填写页面,继续点[验证您的身份]重新填联系信息提交,还是直接关闭填写页面,这时已经陷入死循环无法完成验证。

遇到这种问题直接联系联系苹果客服,选择[会员资格与账户] -> [有关会员资格或账户的其他疑问],然后不管是电话、邮件或者其他方式都行(我选择了发邮件),简单描述一下问题“Apple Developer App联系信息提交后无法完成身份验证”。稍后苹果客服会帮你重置验证身份,再次验证身份会回到第一步的实名认证从头开始。

苹果客服回复我的邮件内容:

验证身份成功后,原先的[验证您的身份]会变为[现在注册],因为当前账号还没处理转让账户持有人请求,所以按钮会是灰色的无法点击。当然,也不需要点击,这个[现在注册]是去完成新的开发者账号注册。

回到开发者网站查看协议同意请求,如此就完成了账户持有人转让。

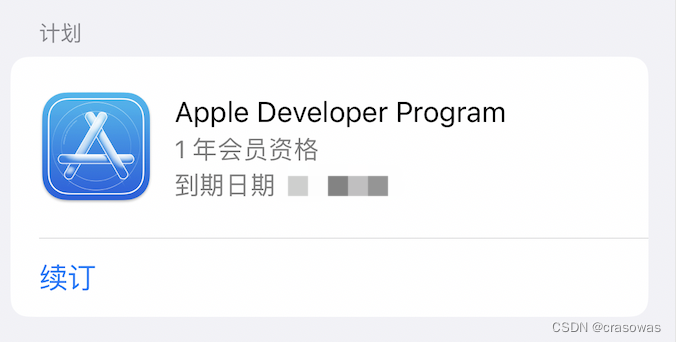

更换订阅的账号

打开Apple Developer App,找到[账户] -> [团队],点进去就可以找到续订按钮:

注意续订过程中使用的订阅账号,后面再续订只能用该订阅账号,不然只能再更换一次。续订成功后,一般都需要将账户持有人转让回去,参考前面转让账户持有人的操作再做一遍即可。

最后

如果这篇文章对你有所帮助,点赞👍加星🌟支持一下吧,谢谢~

本篇文章由@crasowas发布于CSDN。