做网站的是干嘛的黄山旅游最佳时间

进程优先级

首先呢,我们知道一个进程呢(或者也可以叫做一个任务),它呢有时候要在CPU的运行队列中排队,要么有时候阻塞的时候呢又要在设备的等待队列中排队,其实我们排队的本质就是:确认优先级。

关于优先级呢我们可以从以下三个方面来进行说明:

进程优先级是什么?

本质就是得到某种资源的先后顺序。

cpu资源分配的先后顺序,就是指进程的优先权(priority)。

优先权高的进程有优先执行权利。配置进程优先权对多任务环境的linux很有用,可以改善系统性能。

还可以把进程运行到指定的CPU上,这样一来,把不重要的进程安排到某个CPU,可以大大改善系统整体性能。

在Linux操作系统中其实就是PCB中的一个int字段,数值越小,优先级越大。

为什么要有进程优先级?

其实可以用我们生活中的例子来进行说明:

比如说,我们上学的时候要去食堂吃饭,人太多了那你得进行排队,去图书馆的时候你想要有一个好的座位,那你得优先于其他同学占到那个位置,也需要排队,其实要排队的原因就是资源不足!

而你想排队就是想要获得某种资源,而由于资源不足就必须遵循一个先后顺序来获取资源才能够正常运转下去。

Linux中如何操作进程优先级?

Linux进程的优先级数值范围:60~99

Linux进程的默认优先级都是:80

Linux是支持动态优先级调整的

Linux进程PCB中存在一个nice值:进程优先级的修正数据

进程新的优先级= 进程老的优先级+nice值

在linux中可以输入如下命令查看进程的优先级:

ps -la

我们很容易注意到其中的几个重要信息,有下:

UID : 代表执行者的身份

PID : 代表这个进程的代号

PPID :代表这个进程是由哪个进程发展衍生而来的,亦即父进程的代号

PRI :代表这个进程可被执行的优先级,其值越小越早被执行

NI :代表这个进程的nice值

如果我们想要调整一下优先级我们要怎么调整呢?

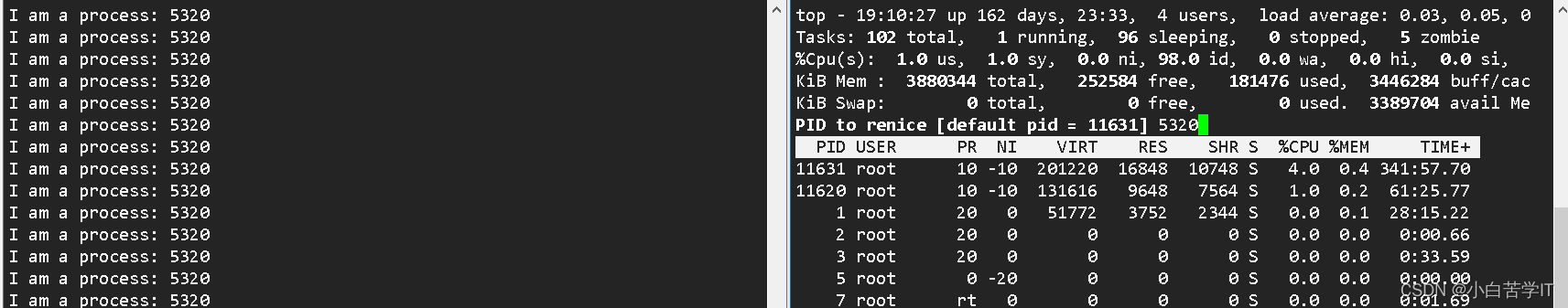

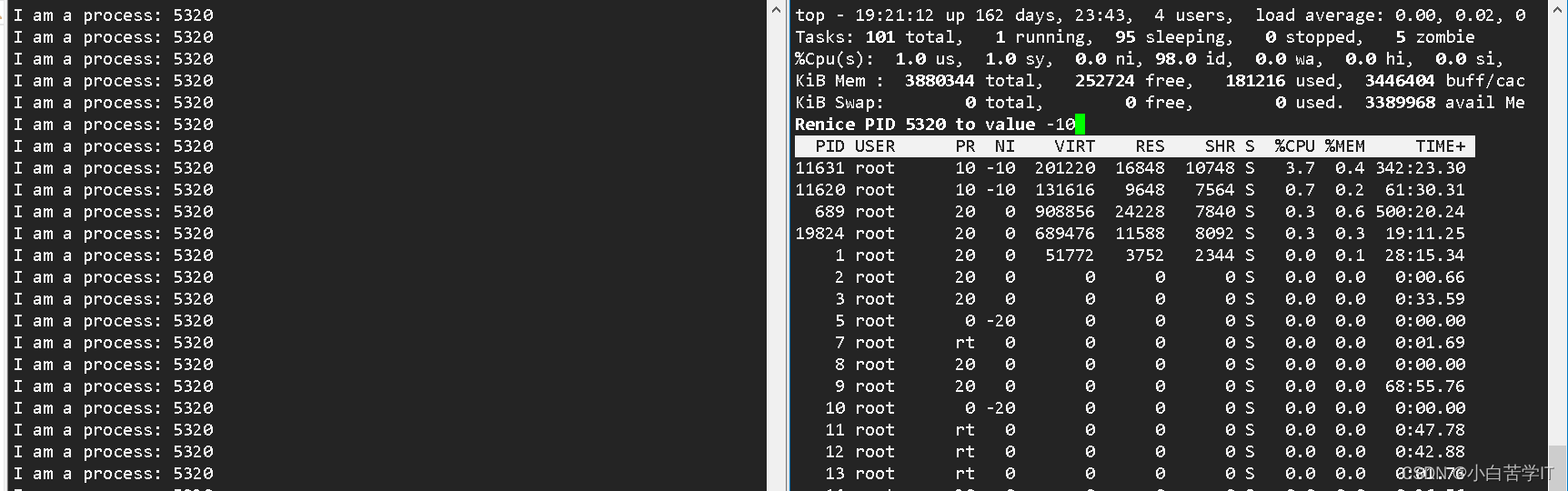

通过top命令启动任务管理器:

然后点击一个r键

当前光标所在这一行就是让我们输入要修改的优先级的进程的pid

比如我这里正在运行一个pid为5230的进程:

我通过输入5230之后,回车:

这里我们要输入的是一个nice值,我们前面说到进程新的优先级=进程老的优先级+nice值,当前进程老的优先级是80,所以我们输入的nice值在老优先级修改的范围必须保证在60-99。

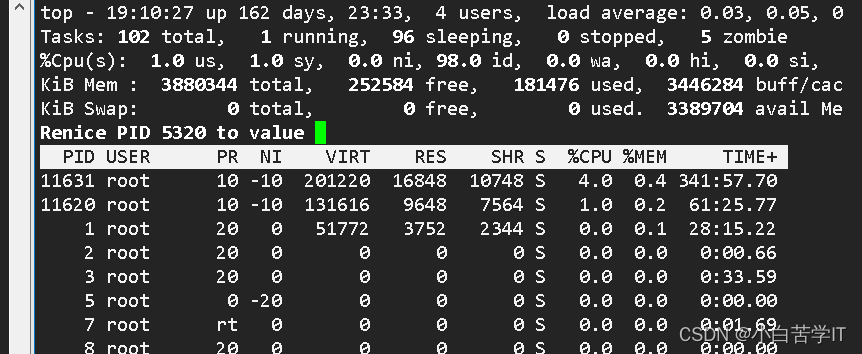

下面我们输入一个10:

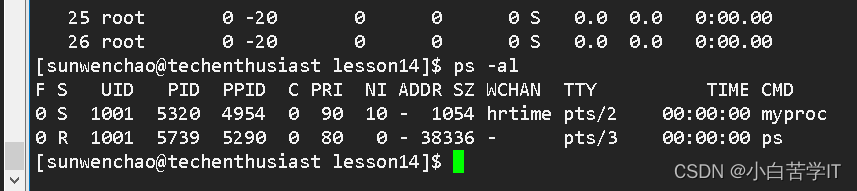

点击q退出任务管理器之后继续输入ps -al命令查看优先级:

发现变成了90了。这里相当于把优先级给调低了。

下面我们把优先级调高一点:

同样的操作,打开任务管理器:

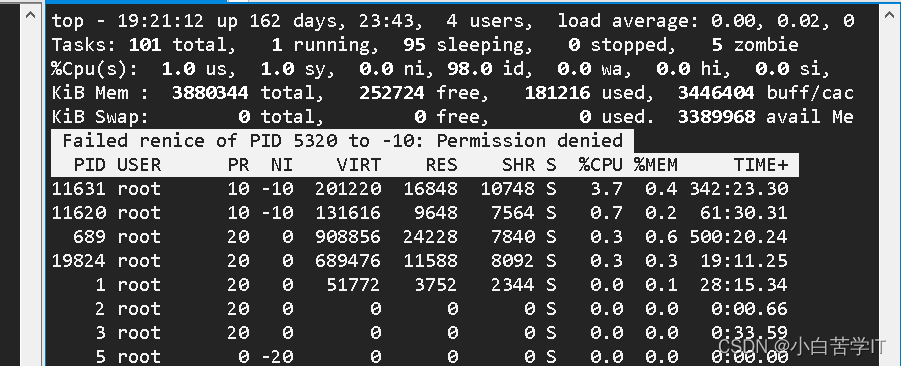

这是我们回车发现我们没有权限,然后我们sudo top提升一下权限输入一下自己的用户密码

然后我们继续进行以上操作,大家是不是会认为,他的优先级这个时候应该是回到80?

那么我们下面来看:

发现我们的这个进程myproc的优先级变成了70.

在我们的Linux当中呢,统一进程要修改优先级的时候老的进程优先级都是从80开始的,所以我们刚刚的老的优先级并不是从90开始变的,而是从80开始-10的,最后变成了70.

所以呢,你要调整优先级每次都是有一个确定的起始值。

nice值调整最小是:-20,超过部分统一当成-20

nice值调整最大是:19,超过部分统一当成19

所以才有刚刚的结论:

Linux进程的优先级数值范围:60~99

PRI也还是比较好理解的,即进程的优先级,或者通俗点说就是程序被CPU执行的先后顺序,此值越小

进程的优先级别越高

那NI呢?就是我们所要说的nice值了,其表示进程可被执行的优先级的修正数值

PRI值越小越快被执行,那么加入nice值后,将会使得PRI变为:PRI(new)=PRI(old)+nice

这样,当nice值为负值的时候,那么该程序将会优先级值将变小,即其优先级会变高,则其越快被执行

所以,调整进程优先级,在Linux下,就是调整进程nice值

nice其取值范围是-20至19,一共40个级别。

那么我们下面来说明为什么要把优先级限定在一定的范围?

如果我们的用户恶意频繁的去修改进程的优先级,一个进程刚调度完,用户又把该进程的优先级设置成最高,一直调度那么有可能就会导致一些优先级比较低的进程就一直不能够被调度,导致一些进程长时间得不到CPU资源,那么我们把这种现象叫做进程饥饿。

OS调度的时候,较为均衡的让每一个进程都能够得到调度。这能够体现出公平性。

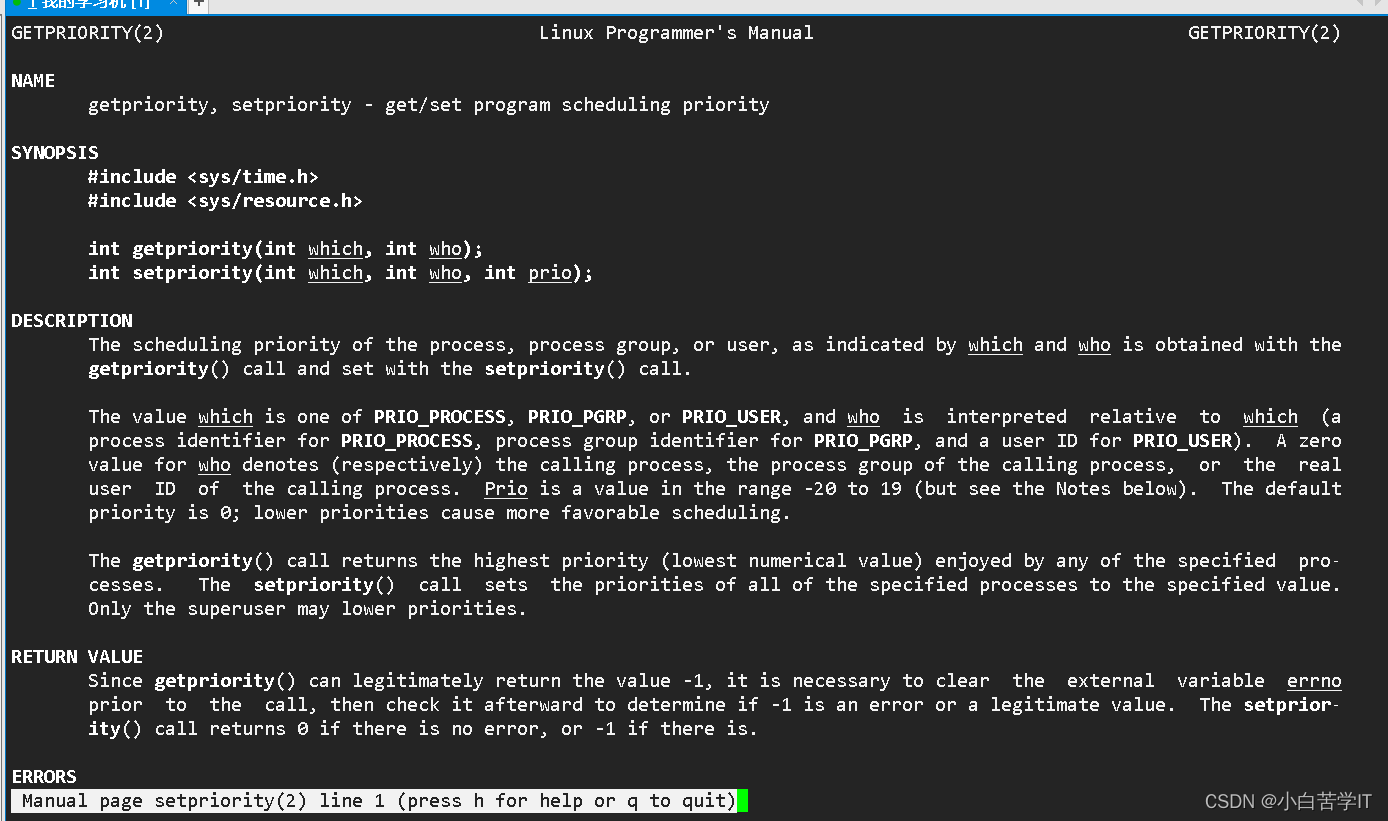

我们linux中呢还有一个关于设置优先级的系统调用接口: