1. 遇到的问题

2. 找到对应VBA文件

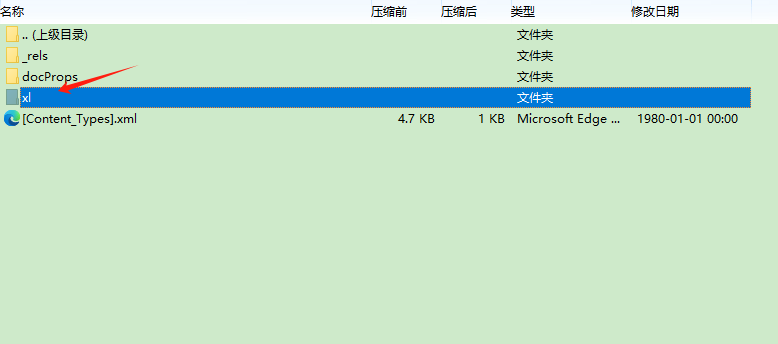

把文件拓展名 xlsm 变为 zip (excel 是高压缩的文件)

报 vbaProject.bin 用 notepad++ 打开

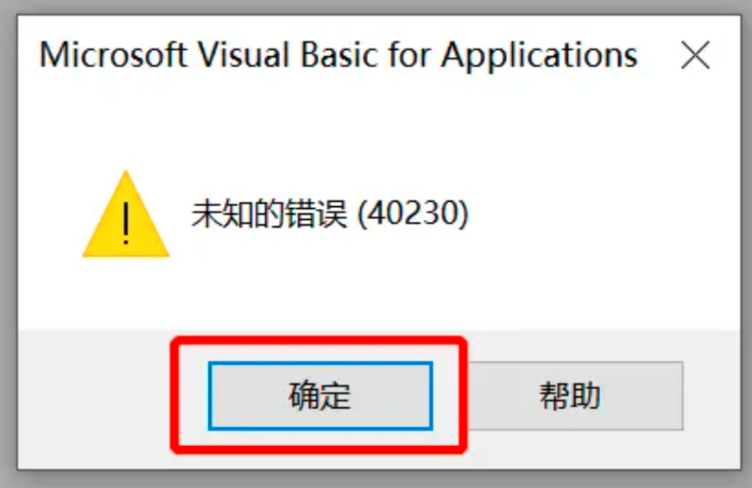

查找到"DPB"

把"DPB"修改为"DPx",注意大小写,保存

然后重新拖进文件夹中,变更成原来的 拓展名即可

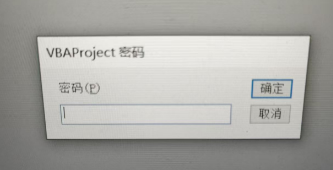

3. 点"开发工具–查看代码":继续弹窗提示,点击确定,知道出现VBAproject界面

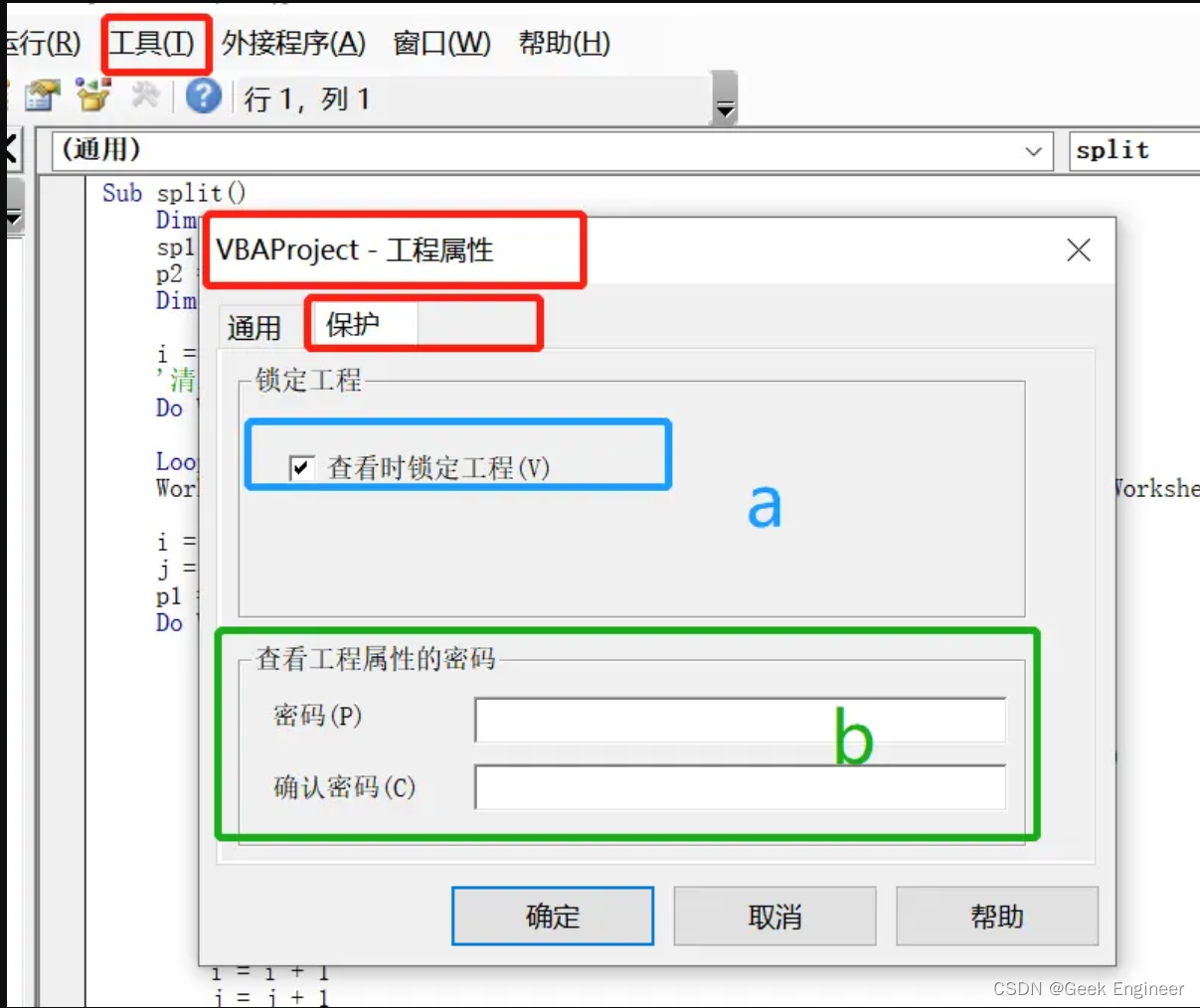

4. 点击:工具 ->VBAProject–>工程属性->保护

a:这里可以选择去掉"查看时锁定工程"前面的勾,这样就没有密码

b:或者重新设置一个新的密码