网站建设支付接口成都网站建制作

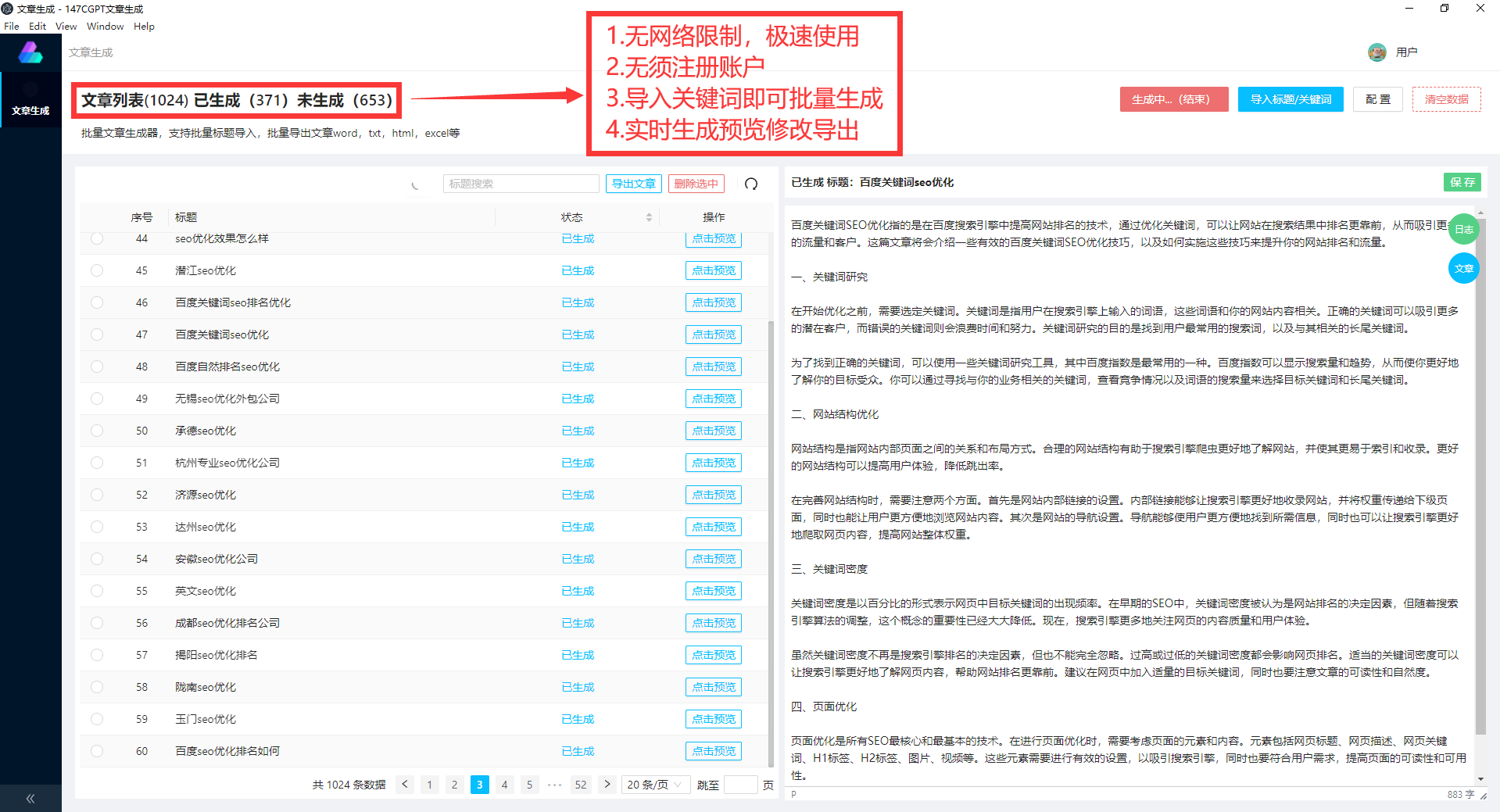

ai文章生成器

AI文章生成器是一种利用人工智能和自然语言处理技术生成文章的工具。它使用先进的算法、机器学习和深度学习技术,深度挖掘和提取大量数据背后的信息,自主学习并合并新的信息,生成优质、原创的文章。

使用AI文章生成器的优点如下:

-

提高创作效率:AI文章生成器能够快速地生成大量的文章,比人工写作更加高效。

-

提高文章质量:AI文章生成器使用人工智能技术,通过对数据背后的潜在信息进行挖掘和分析,生成文章更加准确、专业的细节、可读性、格式和流畅性的。

-

提高内容的专业度:AI文章生成器具备知识领域的专业性和深入度,能够根据用户需求和规范要求,生成内容更为关键的行文效果和语调、个性化适应的信息质量、语言模式、文本类型等。

-

便于使用:AI文章生成器一般具有简单、直观、易上手的界面,并且不需要任何特殊的技术知识即可使用,使用方便快捷。

但是,使用AI文章生成器也有一些需要注意的事项。一些AI文章生成器可能还存在可信度、可靠度和逻辑性的问题,这可能导致生成的文章含有大量错误、不准确的信息,需要进行后期编辑和修订。在使用AI文章生成器生成文章时,需要注意文本的版权和知识产权问题。

总之,AI文章生成器可以为写作者提供有力的支持和优化创作和生产效率,同时也更能满足内容需求,但依然还需要人工编辑和修正,确保文章的质量和有效性。

在线原创文章生成器生成的是原创文章吗

在线原创文章生成器生成的文章通常都是原创文章,因为这些文章是通过基于自然语言处理和人工智能技术的算法生成的,而不是通过复制和粘贴的方式生成的。

然而,在某些情况下,生成的文章可能会与其他文章存在某些相似之处。这可能是由于许多原因造成的,例如,生成的文章可能会受到其所依据的数据集的限制,亦或是算法的不足等等。为了确保文章的原创性及高质量,大多数的在线原创文章生成器会采取一系列的评估措施,从最初的算法设计阶段到最终的文章生成阶段,采取改进方法。

因此,如果您使用一款在线原创文章生成器,并想确保其生成的文章是原创的,请在其上运行专门的检测工具,以确保生成的文章的原创性、正确性和合法性。尽管如此,传统人工写作还是首选,特别是在需要更高的品质、原创性和精准度方面,需注意在线文章生成器的局限性及可能的影响。

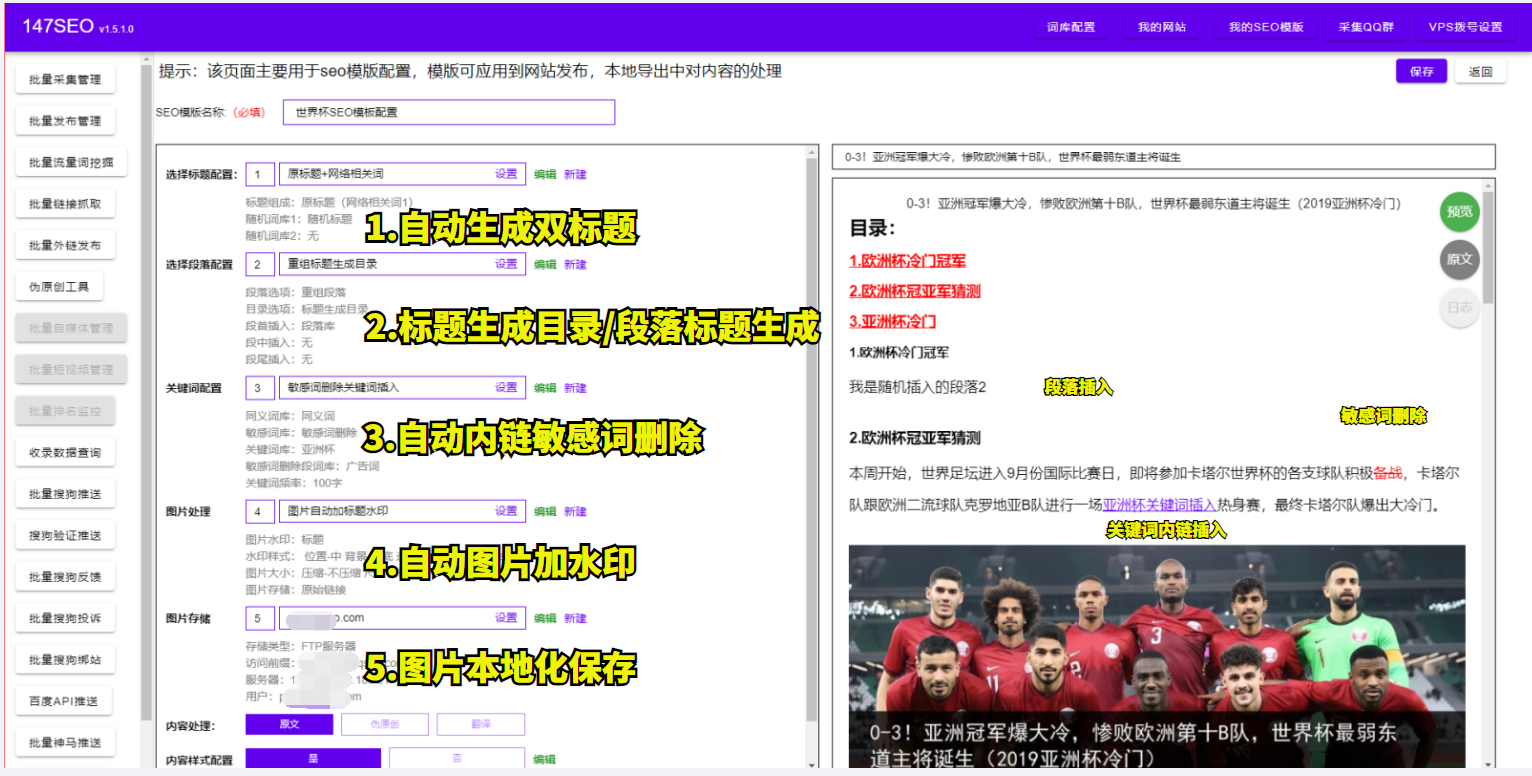

seo文章生成

SEO文章生成是指使用一些在线工具或软件,通过人工智能和自然语言处理技术,自动生成能够帮助网站优化排名的文本和文章。这些文章会根据目标关键词和相关要求生成,以提高网站在搜索引擎结果页面(SERP)中的排名,吸引更多的流量并提高访问者的留存率。

使用SEO文章生成器的优点如下:

-

节省写作时间:使用SEO文章生成器可以快速地生成大量与目标关键词相关的文章,减少写作时间和人力成本。

-

提高搜索排名:SEO文章生成器生成的文章可以更加符合搜索引擎的要求和算法,因而有效地提高了网站的排名。

-

增加网站访问量:通过使用SEO文章生成器生成具有相关性的文章,吸引更多潜在客户浏览网站,并增加网站的流量。

-

提高文章精准度及可读性:生成的seo文章符合其所针对的语境,包括网站建设、品牌宣传和用户需求,提高了搜索用户点击率和满意度。

但需要注意的是,SEO文章生成器可能在某些情况下可能还存在一些问题,例如,生成的文章质量可能不高,不符合品牌要求、SEO关键性,文章字数短、无相关度,可能与想要传达的信息不符,或者有不合适的用语。因此,在使用SEO文章生成器生成文章时,需要事先了解其使用的技术和算法,并进行相应的人工修订和修改,以确保文章的质量、准确性和可读性,及适配品牌的素材要求和讯息。

综合来说,SEO文章生成器可以是一种有用的工具,可以帮助网站优化排名并提高流量,同时需要使用和实践中根据不同需求和数据特点采取最优的解决方案,并注意其带来的潜在问题。