在阿里巴巴做网站什么企业的网络营销策略好写

目录

前言

实现

1、内核配置

2、GDB移植

3、准备调试程序

4、开始调试

前言

gdb调试器是基于命令行的GNU项目调试器,通过gdb工具我们可以实现许多调试手段,同时gdb支持多种语言,兼容性很强。

在桌面 Linux 系统(如 Ubuntu、CentOS 等)上,我们通常可以直接运行 gdb 来调试程序。然而,在嵌入式系统中,由于芯片性能较弱,直接运行 gdb 不太现实(除非是性能较强的嵌入式芯片)。因此,我们通常在 PC 端运行 gdb 工具,源码也在 PC 端,而对应的可执行文件则放在开发板上运行。为了实现这一点,我们需要在开发板上运行gdbserver,通过网络与 PC 端的 gdb 进行通信。因此,要在 PC 上通过 gdb 调试嵌入式程序,需要两个工具:gdb 和 gdbserver,其中 gdb 在 PC 上运行,gdbserver 则需要移植到开发板上运行。

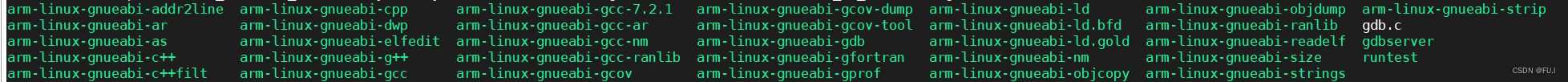

一般的交叉编译器已经自带了GDB工具,主要为:gdb与gdbserver。在交叉编译器安装目录的bin目录内就有这两个工具。需要注意的是,不同的交叉编译工具链编译的可执行文件是不一样的,要注意开发平台上的文件系统编译使用的是什么交叉编译工具链,不然在执行gdbserver的时候会一直报错说找不到文件以及“During startup program exited with code 127”的报错信息。

实现

平台:T113

服务器:Ubuntu 16.04

交叉编译器:gcc-arm-linux-gnueabi

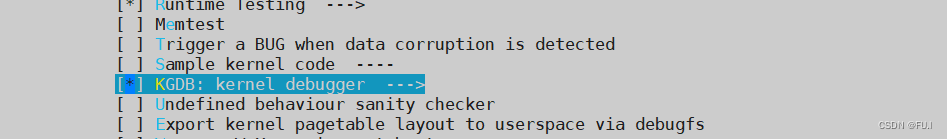

1、内核配置

Kernel hacking --->[*] Kernel debugging[*] KGDB: kernel debugger[*] Compile the kernel with debug info[*] KGDB: use kgdb over the serial console

2、GDB移植

进入交叉编译器安装目录的bin目录内,可以看到里面自带了gdbserver工具,将其放置到开发平台的根文件系统的/usr/bin目录即可。

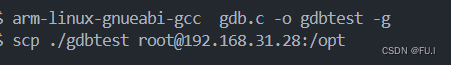

3、准备调试程序

简单编写一个应用程序,使用交叉编译器编译成可执行文件,记得要加上“-g”,表示编译的时候加上调试信息,编译后使用scp传输到开发平台上。

#include <stdio.h>

#include <unistd.h>int main(int argc, char *argv[])

{unsigned int times = 0;for (int i=0; i<5; i++) {printf("runing times:%d\r\n", times);times++;sleep(1);}

}

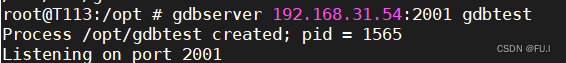

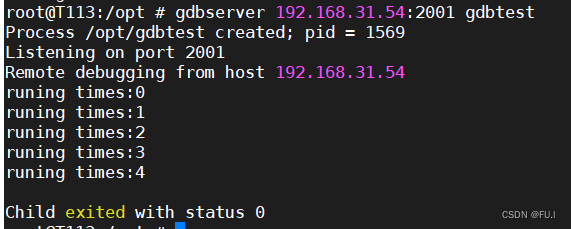

4、在开发平台输入命令开启gdbserver等待PC端连接

gdbserver 192.168.31.54:2001 gdbtest

·gdbserver 工具

·192.168.31.54 PC端IP

·2001 端口 随便整一个

·gdbtest 应用程序

如果输入后报错说找不到文件或者报错“During startup program exited with code 127”那就可能是交叉编译器不对,编译出来的文件不可执行,这是本人遇到的情况。

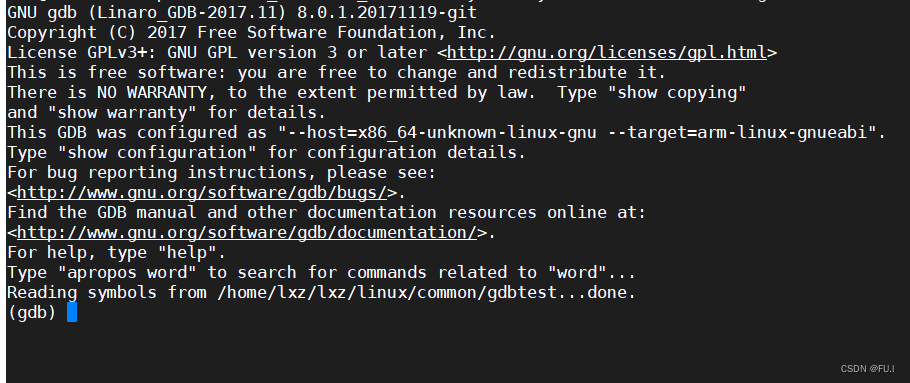

5、PC端运行gdb工具进行调试,运行后就会如下图等待我们输入命令。

./arm-linux-gnueabi-gdb /<具体路径>/gdbtest

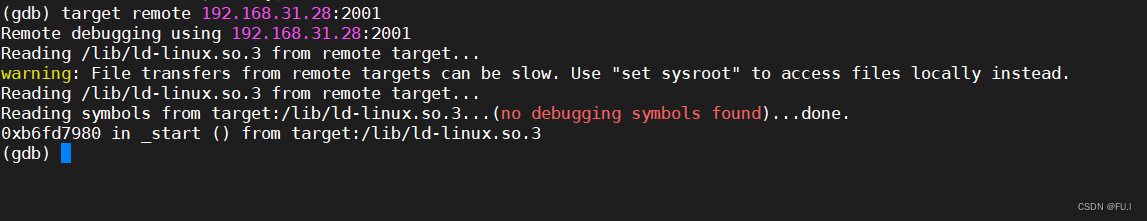

6、连接到开发平台,输入命令连接

//连接到开发板上

target remote 192.168.31.28:2001

·192.168.31.28 开发板IP

·2001 端口

看看开发板的情况,可以看到已经连接上了,接下来就可以进行调试了。

4、开始调试

在调试前先了解一下gdb的命令

| 命令 | 作用 |

| l | 列出所有程序源码 |

| b | 设置断点 |

| c | 运行到断点处 |

| s | 单步运行(会运行到函数里面) |

| n | 单步运行(不会进函数里) |

| p | 打印某个变量值 |

| q | 退出gdb调试界面,运行后开发板上的gdbserver也会停止 |

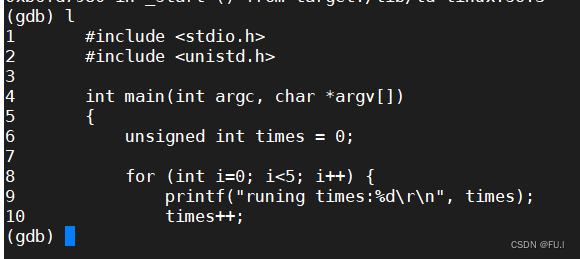

1)列出程序源码

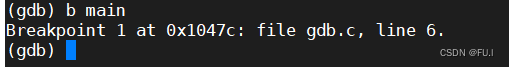

2)设置断点到main函数

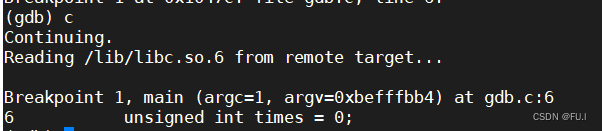

3)运行程序,遇到断点会停下,可以看到停在了main起始位置

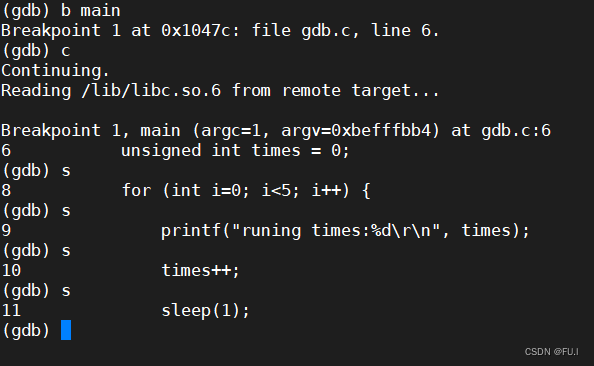

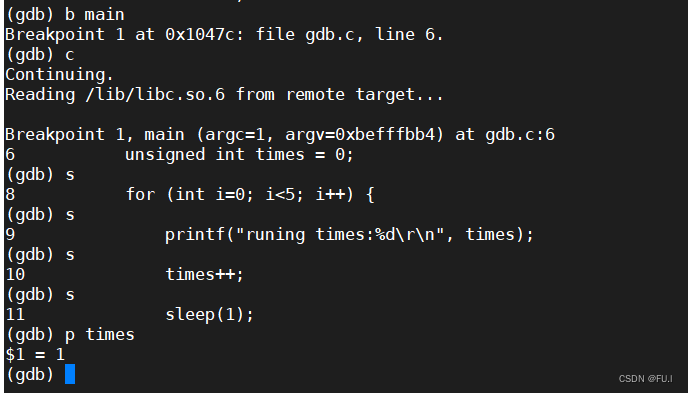

4)单步运行(进函数内),运行四次

5)打印变量值,可以看到已经=1了,因为我们运行过一次完整的循环了

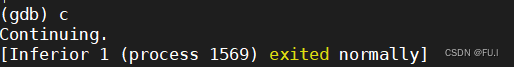

6)自动执行程序,输入命令c,可以看到运行结束了,同时开发板也会打印出调试信息。

7)PC端退出gdb调试

![]()