德州市建设工程质监站网站网页布局设计框架图表

QObject的可重入性:

QThread继承了QObject,它发出信号以指示线程开始或完成执行,并提供一些插槽。

QObjects可以在多个线程中使用发出调用其他线程中槽的信号,并将事件发布到在其他线程中“活动”的对象。这是可能的,因为允许每个线程都有自己的事件循环。

QObject是可以重入的。它的绝大数非GUI子类,如QTimer,QTcpSocket,QUdpSocket和QProcess,都是可以重入的,使得可以从多个线程同时使用这些类。

注意:这些类要在从单个线程中创建和使用,在一个线程中创建对象并从另一个线程调用其函数不能保证有效。需要注意以下3点:

- 必须始终在父级的线程中创建QObject的子级,意味着,除其他事项外,永远不应该将QThread对象(this)作为在线程中创建的对象的父级传导(因为QThread对象本身在另一个线程中创建的)

- 事件驱动对象自能在单一的线程中使用。具体来说,这适用于的定时器和网络模块,例如不可在对象所在线程中QObject::thread()以外的其他线程中启动一个定时器或连接一个套接字。

- 必须确保删除QThread对象以前删除在该线程中创建的所有对象,可以通过在run()函数中的栈上创建对象来确保这一点

虽然QObject是可重入的,但GUI类,特别是QWidget以及其子类,都是不是可重入的,它们只能从主线程中使用QCoreApplication::exec()也需要在主线程中调用。

实际上,可以通过将耗时的操作放在单独的工作线程中并在工作线程完成后在主线程的屏幕上显示结果, 可以轻松解决在主线程以外的其他线程中使用 GUI 类的不可能性。

通常,不支持在 QApplication 之前创建 QObjects,这可能会导致退出时出现奇怪的崩溃,具体取决于平台。这意味着 QObject 的静态实例也不受支持的。结构合理的单线程或多线程应用程序应使 QApplication 成为第一个创建,最后一个销毁的 QObject。

每个线程的事件循环:

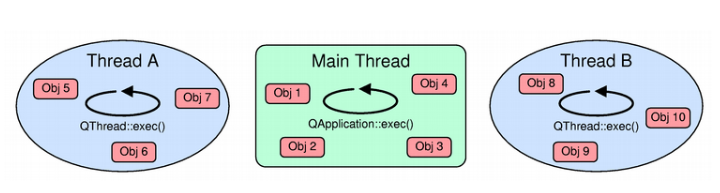

每个线程都可以有自己的事件循环。

初始线程使用 QCoreApplication::exec() 启动其事件循环,或者对于单对话框 GUI 应用程序,有时使用 QDialog:exec()。其他线程可以使用 QThread::exec() 启动事件循环。与QCoreApplication一样,QThread提供了一个exec()函数和一个quit()插槽。

线程中的事件循环使线程可以使用某些需要存在事件循环的非 GUI Qt 类,它还可以将来自任何线程的信号连接到特定线程的插槽。

QObject实例被称为驻留在创建它的线程中。该对象的事件由该线程的事件循环调度,QObject中的线程可以使用QObject::thread()使用。可以使用QObject::moveToThread()函数更改对象其子线程相关性。

从拥有对象的线程以外的线程调用QObject是不安全的,除非能保证该对象当时不处理事件。改用QObject::deleteLater(),将发布一个DeferredDelete事件,对象线程的事件循环最终将拾取该事件。默认情况下,拥有 QObject 的线程是创建 QObject 的线程,但在调用QObject::moveToThread() 之后则不是

如果未运行任何事件循环,则不会将事件传递到对象。例如,如果您在线程中创建了一个 QTimer 对象,但从不调用 exec(),则 QTimer 将永远不会发出其 timerout() 信号。调用 deleteLater 也不起作用。(这些限制也适用于主线程。)

所有线程都支持事件过滤器,但限制是监视对象必须与受监视对象位于同一线程中.

从其他线程中访问QObject子类:

QObject 和它所有的子类都不是线程安全的,这包括整个事件传递系统。需要时刻记着,正在从其他线程中访问一个对象时,事件循环可能正在向这个对象传递事件。

如果调用一个没有在当时线程中的QObject子类的函数,而这个对象有可能会获取事件,那么就必须使用mutex来保护对这个QObject子类的内部数据的所有访问,否者,可能出现崩溃或则其他以外行为。

与其他对象像是,QThread对象,居住于常见该对象的线程。在QThread子类中提供槽一般时不安全的,除非使用mutex来保护成员变量。但是,可以安全地在Qthread::run函数中发射信号,因为信号发射是线程安全的。

跨越线程的信号与槽:

Qt支持以下信号与槽连接类型

可已通过向connect()函数传递附加的参数来指定关联类型,注意,如果在接收者线程中由一个事件循环,那么当发送者与接收者在不同的线程中时,使用Direct Connection是不安全的,类似的,调用其他线程中的对象的任何函数也是不安全的。

QObject::connect() 是线程安全的

- Auto Connection(自动连接,默认),如果在接收对象具有关联的线程中发出信号,则行为与直接连接相同。否则,该行为与排队连接相同。

- Dirct Connection(直接连接)会立即调用该插槽。插槽在发射器的线程中执行,该线程不一定是接收器的线程。

- Queued Connection(排队连接)当控制返回到接收器线程的事件循环时,将调用该槽。该插槽在接收器的线程中执行。

- Blocking Queued Connection(阻止排队连接)

- 该槽的调用方式与排队连接一样,但当前线程块除外,直到槽返回。(使用此类型连接同一线程中的对象将导致死锁。)

- Unique Connection(唯一连接)该行为与自动连接相同,但仅当它不复制现有连接时,才会建立连接。即,如果同一信号已经连接到同一对对象的同一插槽,则不会建立连接并且 connect()

参考文档:

Threads and QObjects | Qt 5.15