北京工程建设质量协会网站手机网站用什么软件开发

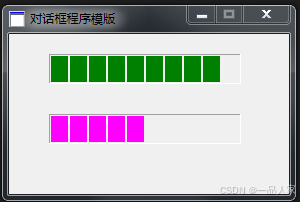

;运行效果

;win32汇编环境,对话框程序中使用进度条控件

;进度条控件主要涉及的是长度单位,每步步长,推进的时间。

;比如你的长度是1000,步长是100,每秒走1次,则10秒走完全程

;比如你的长度是1000,步长是10,每秒走1次,则100秒走完全程,但每格格子的长度与上面一样

;以下例子设置为2条进度条,通过比较,可以理解其原理。

;下面为asm文件

;>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

.386

.model flat,stdcall

option casemap:none

;>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>&g