网站托管维护代运营电脑安装wordpress

文章目录

- 一、今日成绩

- 二、错题总结

- 第一题

- 第二题

- 第三题

- 三、知识查缺

题目及解析来源:2023年05月10日软件设计师每日一练

一、今日成绩

二、错题总结

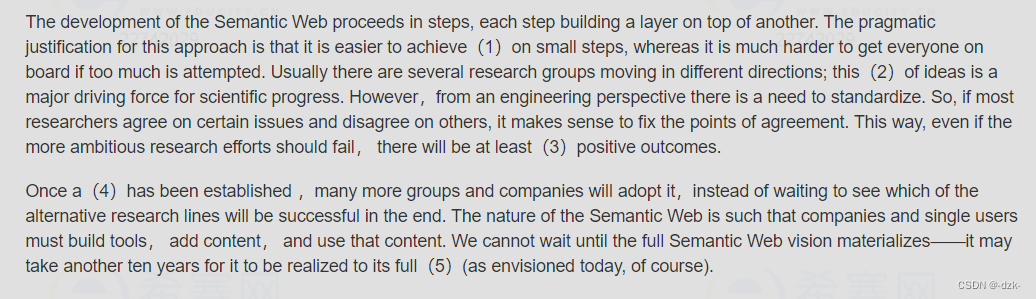

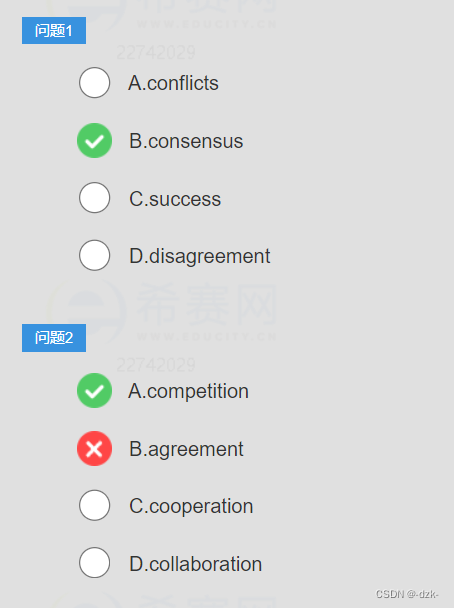

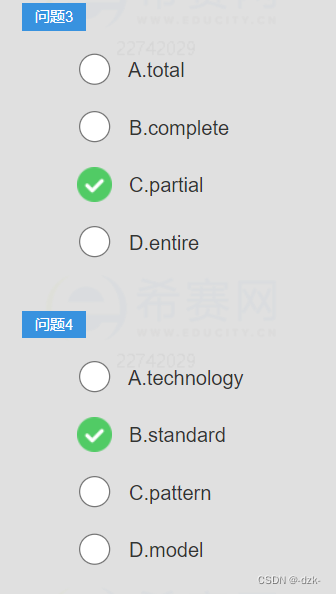

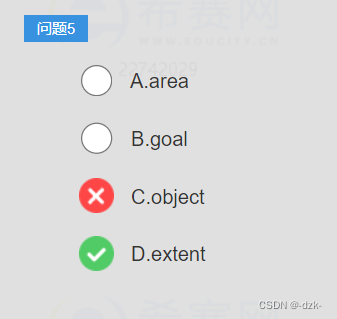

第一题

解析:

proceed v.开始行动,开展;继续做(或从事、进行)

layer n.层次;等级

pragmatic adj.讲求实际的,务实的

justification n.正当理由,合理解释

whereas conj.但是,然而

perspective n.视角,观点;角度

scientific adj.科学的;细致严谨的

standardize v.使标准化

alternative n.可供选择的事物,替代物;adj.可替代的,备选的

materialize v.实现;突然显现

envision v.想象,预想

conflict n.争执,分歧;抵触,矛盾

consensus n.一致看法,共识

disagreement n.分歧,争论;不符,不一致

competition n.竞争;比赛

agreement n.协议;共识,同意

cooperation n.合作;协助

collaboration n.合作,协作

model n.模型;模式

pattern n.模式,方式

object n.物体,事物;目的,目标

extent n.程度;范围

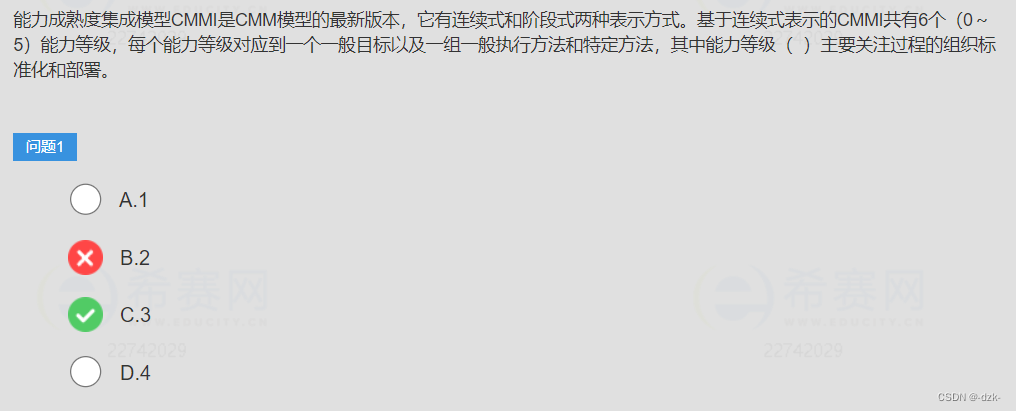

第二题

解析:

CMMI模型中 CL3(已定义级的):其共性目标集中于已定义的过程的制度化。过程是按照组织的剪裁指南从组织的标准过程集中剪裁得到的,还必须收集过程资产和过程的度量,并用于将来对过程的改进(关注 过程的组织级标准化和部署)。

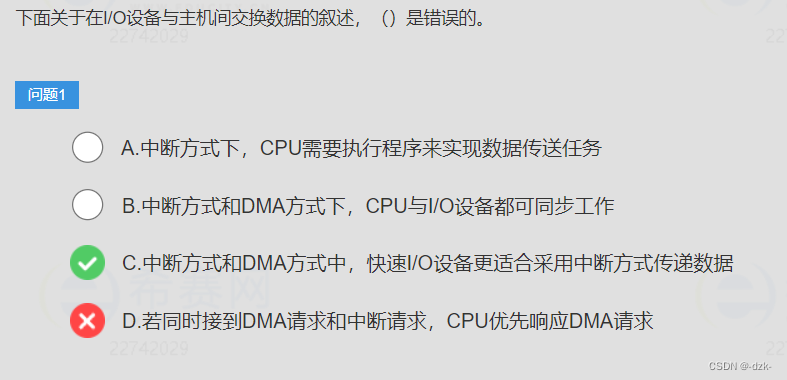

第三题

解析:

中断方式 中CPU需要在得到通知后,保存现场,然后再转入I/O中断服务程序的执行,完成与I/O系统的数据交换,然后再返回被打断的程序继续执行。其过程中需要执行若干条指令才能处理一次中断时间,这种方式无法满足高速的批量数据传送要求。

DMA传送方式的优先级高于程序中断,两者的区别主要表现在对CPU的干扰程度不同。中断请求不但要使CPU停下来,而且要CPU执行中断服务程序为中断请求服务,这个请求包括了对断点和现场的处理以及CPU与外设的传送,所以CPU付出了很多的代价;DMA请求仅仅使CPU暂停一下,不需要对断点和现场处理,并且是由DMA控制外设和主存之间的数据传送,无须CPU的干预,DMA只是借用了一点CPU的时间而已。所以 DMA传送方式的优先级高于程序中断。若同时接到DMA请求和中断请求,CPU优先响应DMA请求。

三、知识查缺

- 复习 软件维护相关概念 相关知识(软件维护工具 主要有:版本控制工具;文档分析工具;开发信息库工具;逆向工程工具;再工程工具;配置管理支持工具)。

- 视频信息是连续的图像序列,帧 是构成视频信息的基本单元。

- 复习 主存编址计算 相关知识。

- 在ASP的内置对象中,response 对象可以修改cookie中的值。

- 复习 关系代数 相关知识。

- 复习 队列与栈 相关知识。

- 复习 二叉树的遍历 相关知识。