户型图在线设计网站网站公司怎么做的好处

自然语言处理(NLP) 是对使计算机能够处理、分析、解释和推理人类语言的技术和工具的研究和应用。 NLP 是一个跨学科领域,它结合了语言学和计算机科学等领域已建立的技术。 这些技术与人工智能结合使用来创建聊天机器人和数字助理,例如 Google Assistant 和亚马逊的 Alexa。

让我们花一些时间来探讨自然语言处理背后的基本原理、NLP 中使用的一些技术以及 NLP 的一些常见用例。

为什么自然语言处理 (NLP) 很重要

为了让计算机解释人类语言,必须将它们转换成计算机可以操作的形式。 然而,这并不像将文本数据转换为数字那么简单。 为了从人类语言中获取含义,必须从构成文本文档的数百或数千个单词中提取模式。 这不是一件容易的事。 几乎没有什么硬性规则可以应用于人类语言的解释。 例如,根据上下文的不同,完全相同的一组单词可能意味着不同的事物。 人类语言是一种复杂且常常含糊不清的东西,一个陈述可以是真诚的,也可以是讽刺的。

尽管如此,在解释单词和字符时可以使用一些通用准则,例如字符“s”用于表示某个项目是复数。这些一般准则必须相互配合使用,才能从文本中提取含义,创建机器学习算法可以解释的特征。

自然语言处理涉及能够获取非结构化数据并将其转换为结构化数据的各种算法的应用。如果这些算法以错误的方式应用,计算机通常无法从文本中得出正确的含义。这通常可以在不同语言之间的文本翻译中看到,其中句子的精确含义经常会丢失。尽管机器翻译在过去几年里有了很大的进步,但机器翻译错误仍然频繁发生。

自然语言处理 (NLP) 技术

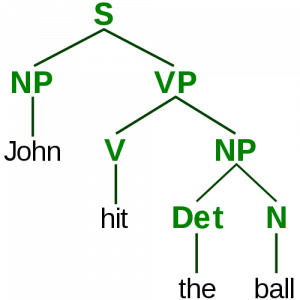

照片: Tamur 来自 WikiMedia Commons,公共领域 (https://commons.wikimedia.org/wiki/File:ParseTree.svg)

许多 技术 自然语言处理中使用的术语可以分为两类之一:语法或语义。 语法技术是处理单词顺序的技术,而语义技术是涉及单词含义的技术。

语法 NLP 技术

语法示例包括:

- 合法化

- 形态分割

- 词性标注

- 解析

- 断句

- 词干

- 分词

词形还原是指将单词的不同变形提炼为单一形式。 词形还原将时态和复数等事物简化,例如,“feet”可能变成“foot”,“stripes”可能变成“stripe”。 这种简化的单词形式使算法更容易解释文档中的单词。

形态分割是将单词划分为词素或单词的基本单位的过程。 这些单位都是免费的 语素 (可以单独作为单词)和前缀或后缀。

词性标注 只是识别输入文档中每个单词属于哪个词性的过程。

解析 是指分析句子中的所有单词,并将它们与其正式语法标签相关联或对所有单词进行语法分析。

断句,或 句子边界分割, 指决定句子的开始和结束位置。

词干 是将单词简化为单词的根形式的过程。 例如,connected、connection、connections 都会被词干为“connect”。

分词 是将大块文本分成小单元的过程,这些小单元可以是单词或词干/词形还原单元。

语义 NLP 技术

语义 NLP 技术包括以下技术:

- 命名实体识别

- 自然语言生成

- 词义消歧

命名实体识别 涉及标记某些可以放入多个不同预设组之一的文本部分。 预定义的类别包括日期、城市、地点、公司和个人等。

自然语言生成 是使用数据库将结构化数据转换为自然语言的过程。 例如,有关天气的统计数据,如温度和风速,可以用自然语言进行概括。

词义消歧是根据单词出现的上下文为文本中的单词赋予含义的过程。

NLP 深度学习模型

常规多层感知器无法处理顺序数据的解释,其中信息的顺序很重要。 为了处理顺序数据中顺序的重要性,使用了一种神经网络来保留训练中先前时间步的信息。

递归神经网络 神经网络的类型 循环之前时间步的数据,在计算当前时间步长的权重时将它们考虑在内。本质上,RNN 具有在前向训练过程中使用的三个参数:基于先前隐藏状态的矩阵、基于当前输入的矩阵以及隐藏状态和输出之间的矩阵。由于 RNN 可以考虑之前时间步的信息,因此在解释单词的含义时,它们可以通过考虑句子中较早的单词来从文本数据中提取相关模式。

另一种用于处理文本数据的深度学习架构是 长短期记忆 (LSTM) 网络。 LSTM 网络在结构上与 RNN 相似,但由于其架构上的一些差异,它们往往比 RNN 表现得更好。 它们避免了使用 RNN 时经常出现的一个特定问题,称为 梯度爆炸问题。

这些深度神经网络可以是单向的,也可以是双向的。 双向网络不仅能够考虑当前单词之前的单词,还能够考虑当前单词之后的单词。 虽然这会带来更高的精度,但计算成本更高。

自然语言处理 (NLP) 用例

由于自然语言处理涉及人类语言的分析和操作,因此它具有极其广泛的应用范围。 NLP 的可能应用包括聊天机器人、数字助理、情绪分析、文档组织、人才招聘和医疗保健。

聊天机器人和数字助理(例如亚马逊的 Alexa 和 Google Assistant)是语音识别和合成平台的示例,它们使用 NLP 来解释和响应声音命令。 这些数字助理可以帮助人们完成各种任务,让他们将一些认知任务转移到另一台设备上,并释放一些脑力来处理其他更重要的事情。 我们可以让我们的数字助理来做这件事,而不是在忙碌的早晨查找去银行的最佳路线。

情绪分析 是使用 NLP 技术来研究人们对某种现象的反应和感受,并通过他们使用语言来传达。 捕捉声明的情绪,例如解释产品评论是好是坏,可以为公司提供有关其产品如何被接受的大量信息。

自动组织文本文档是 NLP 的另一个应用。 谷歌和雅虎等公司使用 NLP 算法对电子邮件文档进行分类,将它们放入适当的分类中,例如“社交”或“促销”。 他们还使用这些技术 识别垃圾邮件 并阻止它到达您的收件箱。

一些团体还开发了 NLP 技术,用于识别潜在的职位招聘,并根据相关技能找到他们。 招聘经理还使用 NLP 技术来帮助他们对申请人列表进行排序。

NLP 技术也被用于增强医疗保健。 NLP 可用于改善疾病的检测。 可以通过 NLP 算法分析健康记录并提取症状,然后用于建议可能的诊断。 亚马逊的 Comprehend Medical 平台就是一个例子,该平台可以分析健康记录并提取疾病和治疗方法。 NLP 的医疗保健应用还扩展到心理健康。 有应用程序 比如沃博t,它向用户介绍了基于认知行为疗法的各种焦虑管理技术。