西安自助建站做网站响应式企业网站源码

由于需要在 linux 机器上完成 node 项目的构建,需要安装 nodejs, 想着不同项目需要使用不同的版本,索性安装一下 nvm 吧,因为之前在 windows 上已经安装过 nvm-windows, 应该很容易上手,我尝试了官网提供的几种方式,最后把我觉得最靠谱的方式分享给大家。

官网:GitHub - nvm-sh/nvm: Node Version Manager - POSIX-compliant bash script to manage multiple active node.js versions

快速安装

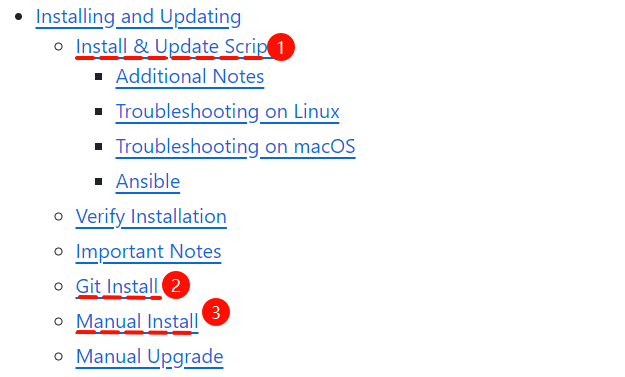

官网提供了几种安装方式:

-

Install & Update by Script, 通过 sh 脚本安装

-

Git Install,通过 git 仓库安装

-

Manual Install, 手动安装

三种方式,其实本质就是把项目仓库下载到本地,配置相关的环境变量,执行一些脚本而已。

我将我安装的过程分享给大家,主要分 3 步:

-

git clone 项目到目录

-

git checkout 最新版本的 tag

-

source 配置命令到 bash 上下文

也不一定非要 git clone ,直接下载解压也是可以的,本质是下载项目到某个目录。

我这里直接 clone 到 ~/.nvm 目录

# 可选,会自动创建目录

mkdir ~/.nvm

# 克隆到指定目录,也可以直接下载解压到目录也可以(访问限制的场景有用)

git clone git@github.com:nvm-sh/nvm.git ~/.nvm

export NVM_DIR="$HOME/.nvm"

cd $NVM_DIR

# 可选,用 master 分支也不是不可以

git checkout v0.40.1

# 使 nvm 命令加到 PATH 中,可以直接使用

. ./nvm.shnvm --version

上面的安装比较简单,记住只需要把项目下下来即可。

配置命令补全

为了下次再打开终端也能有 nvm 命令,需要配置一下 .bashrc 或者 /etc/profile 都可以,不然找不到 nvm 命令,缺少命令自动补全功能。

# 我这里直接添加到了用户下的 .bashrc 文件中

vim ~/.bashrc#...追加如下部分内容

export NVM_NODEJS_ORG_MIRROR=https://npmmirror.com/mirrors/node/

export NVM_DIR="$HOME/.nvm"

[ -s "$NVM_DIR/nvm.sh" ] && \. "$NVM_DIR/nvm.sh" # This loads nvm

[ -s "$NVM_DIR/bash_completion" ] && \. "$NVM_DIR/bash_completion" # This loads nvm bash_completion# 配置完可以重新打开终端窗口,验证是否有 nvm 命令

nvm --version

安装 nodejs

# 列出当前远程仓库支持的版本

nvm ls-remote

# 安装最新的 lts 版本

nvm install --lts

# 安装 14 版本

nvm install 14

# 安装 16 版本

nvm install 16

# 列出当前版本

nvm current

# 卸载指定版本

nvm uninstall 16

配置 npm 加速

配置 npm 加速比较简单: npmmirror 镜像站

npm config set registry https://registry.npmmirror.com

nvm 卸载

nvm 的卸载也比较简单,直接删除相关文件和配置项即可

# 清除 bash 终端命令补全(可选,把下面的 .bashrc 中的内容删掉,新终端里就不会有 nvm 相关命令了了)

nvm unload

# 删除目录

rm -rf $NVM_DIR

# 删掉之前配置的环境变量及 bash 补全的内容

vim ~/.bashrc