江西网站开发方案贵州企业展示型网站建设

文章目录

- 一、前言

- 二、云耀云服务器L实例要点介绍

- 2.1 什么是云耀云服务器L实例

- 2.1.1 浅析云耀云服务器L实例

- 2.2 云耀云服务器L实例的产品定位

- 2.3 云耀云服务器L实例优势

- 2.4 云耀云服务器L实例支持的镜像与应用场景

- 2.5 云耀云服务器L实例与弹性云服务器(ECS)区别

- 2.6 切换云耀云服务器L实例的镜像操作系统

- 三、购买与配置云耀云服务器L实例

- 四、宝塔应用搭建

- 4.1 资源概览

- 4.2 宝塔应用搭建

- 4.2.1 重置密码

- 4.2.2 配置安全组

- 4.2.3 验证登录宝塔页面

- (1)访问并登陆宝塔

- (2)查看宝塔默认密码

- (3)修改宝塔默认密码

- 五、文末总结

一、前言

企业迁移至云端时,首要难题在于如何正确选用云服务器。鉴于市面上琳琅满目的云服务器产品,中小型企业以及初阶开发者常常陷入选择困境之中。同时,传统云服务器的部署流程复杂,运维要求高,费用居高不下,这显著妨碍了中小企业实现云端化的目标。在2023年 8 月27 日,华为云与其生态伙伴共同举办的第二届 828 B2B 企业节开幕式上,华为云隆重推出了一系列新产品和解决方案,其中包括了华为云云耀云服务器L实例等数十款精品。本文主要针对这次的新产品:【云耀云服务器L实例】进行使用教学进行详细讲解

二、云耀云服务器L实例要点介绍

2.1 什么是云耀云服务器L实例

云耀云服务器L实例是新一代开箱即用、面向中小企业和开发者打造的全新轻量应用云服务器。云耀云服务器L实例提供丰富严选的应用镜像,实现应用一键部署,助力客户便捷高效的在云端构建电商网站、Web应用、小程序、学习环境、各类开发测试等。

作为专门为中小企业和开发者群体度身打造的云服务产品,华为云云耀云服务器L实例以其出色的性能、简便的上手流程和省心的管理方式而脱颖而出。它将为中小企业和开发者提供崭新的云上体验,只需三个简单步骤,性能翻倍提升,帮助中小企业用户轻松跨出进军云端的第一步。无论是建立企业网站、小程序后台,还是搭建电商平台、部署企业业务系统,亦或者构建线上开发测试环境,华为云云耀云服务器L实例均可助您快速搭建云服务,削减成本,提升工作效率。

2.1.1 浅析云耀云服务器L实例

更新于:09/04/2023 21:13

要不是我在研究怎么切换华为云云耀云服务器L实例的镜像,可能不会过于注意这些细节。在云耀云服务器L实例控制台退订页面中可以看到一个产品列表(如下图),在这个页面可以看出,实际上云耀云服务器L实例是一个产品包,这个产品包绑定了其中包括镜像、固定带宽、云主机以及云硬盘的一个资产包。而这些资产包绑定在一起,就组成了云耀云服务器L实例,这些资产包也就是你在最初购买的时候所选择。

2.2 云耀云服务器L实例的产品定位

云耀云服务器L实例使用门槛较低,如果您是正在了解云计算服务的入门用户,或是需要在服务器中部署简单应用的个人开发者、中小企业,那么推荐您选择云耀云服务器L实例。

从产品定位中可以看出,如果是中小企业,或者是个人开发者,无疑云耀云服务器L实例是一个非常好的选择。

2.3 云耀云服务器L实例优势

对于云耀云服务器L实例优势,在华为云官网以及云耀云服务器L实例手册中已经有很多的描述,博主这里整理后总结为:

智能性能:搭载华为云擎天架构和AI算法智能调度,确保流畅性能,无卡顿体验。全球存算网络保证超低时延,适用于低网络延迟场景。

价值优势:出色的性价比,门槛极低,多种实例规格可供选择,平衡性能与成本,有力支持初创企业和开发者。

简易上手:提供多种高品质镜像,经过官方测试,覆盖各种场景,预置模板,便于快速搭建应用。自动化编排和向导式应用搭建简化了操作流程,使上云变得更加容易。

管理省心:可视化管理工具使资源和业务架构透明化。提供贴心的服务状态提醒,一键式资源续退操作,实现了极简管理。实时监控资源负载和安全,确保服务永远在线。此外,华为云还提供多种安全服务,包括备份和主机安全,为用户提供最高级别的安全防护。

2.4 云耀云服务器L实例支持的镜像与应用场景

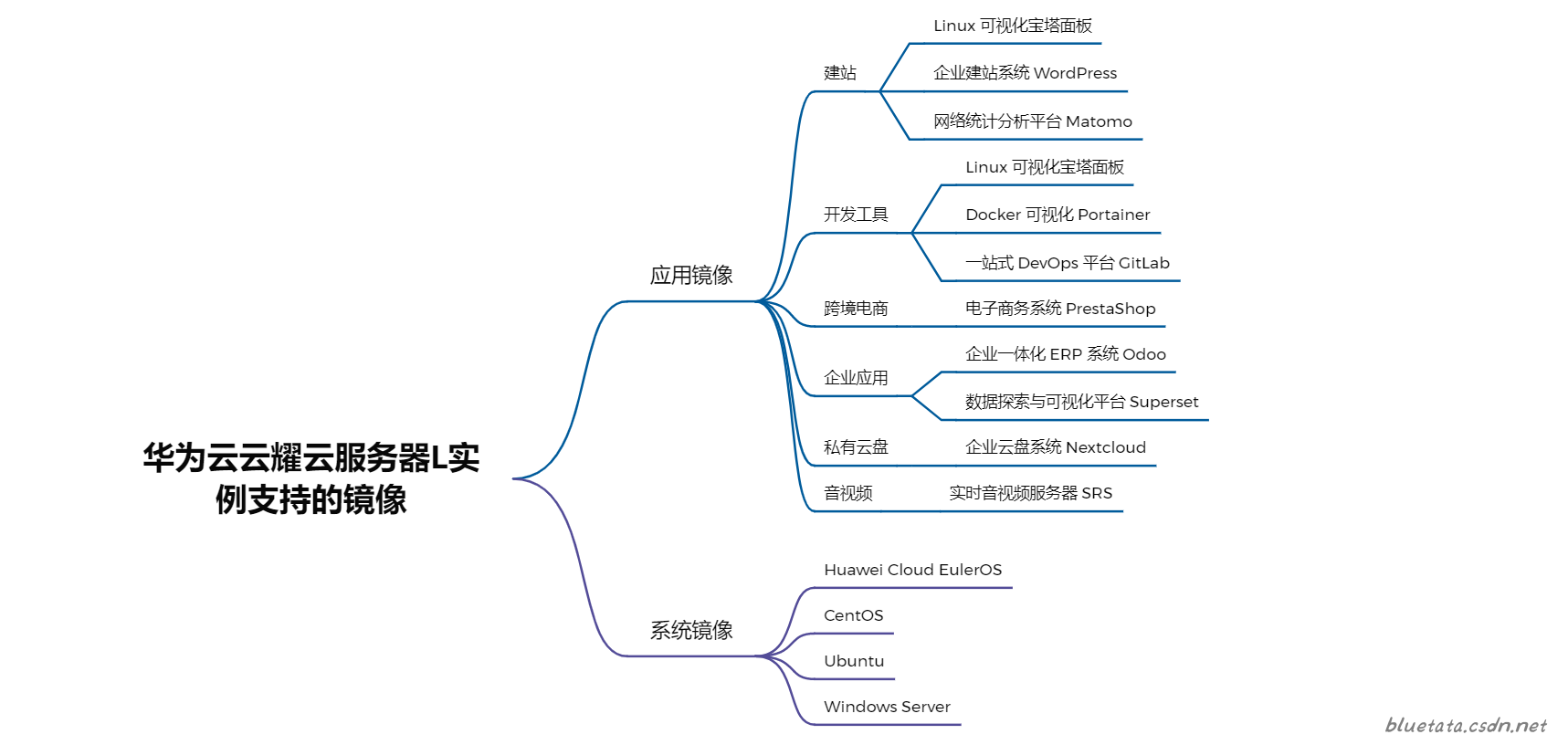

云耀云服务器L实例适用于支撑小型网站、Web应用、博客、论坛、云端开发环境等轻量级、低负载且访问量适中的应用场景。很大的程度上对于云耀云服务器L实例使用的场景得益于它所支持的镜像,根据下面的导图可以看到所支持的镜像如下:

从上述云耀云服务器L实例支持的镜像的脑图中可以看出,云耀云服务器L实例主要可以分为两类镜像,一种是传统的系统镜像,包括华为的 EulerOS和常见的Linux镜像 CentOS 与 Ubuntu,还有Windows Server。另一种是根据常见的应用场景,所支持的应用镜像,种类比较多,基本可以分为这几类:建站、开发工具、跨境电商、企业应用、私有云盘、音视频。

2.5 云耀云服务器L实例与弹性云服务器(ECS)区别

云耀云服务器L实例与ECS的主要区别:

-

云耀云服务器L实例简化了购买和配置流程,提供一站式的综合功能,包括网络配置、云硬盘、云备份、主机安全等,适用于快速搭建简单应用,特别适用于低负载应用场景,能够更加便捷、高效地部署和管理应用。

-

弹性云服务器(ECS)提供多种计费模式、规格类型、镜像类型和磁盘类型,允许用户根据不同的业务需求自定义配置弹性云服务器。它更适用于高负载应用场景,以确保性能的稳定性。

最终你选择云耀云服务器L实例还是ECS取决于你的具体需求。如果需要简化的购买和配置流程以及适用于低负载应用场景的高效部署,云耀云服务器L实例可能是更好的选择。而对于需要更高度定制化和性能稳定性的应用,ECS可能更合适。

2.6 切换云耀云服务器L实例的镜像操作系统

更新于 09/04/2023 21:24

在华为云云耀云服务器L实例的官方文档中有写到,现阶段暂时不支持切换镜像,官方链接:点击这里

如果你是真的是必要的需要切换操作系统,那么你可以参考一下我的另一个博文:

解决办法:[ 云计算 华为云 ] 解决办法:如何更换华为云云耀云服务器L实例的镜像

三、购买与配置云耀云服务器L实例

购买与配置云耀云服务器L实例是开头的第一步,它将帮助您轻松启动云计算资源,满足您的应用需求。在本部分,我们将详细讨论如何获取和设置云耀云服务器L实例,为您提供实用的指导和建议。

进入华为云官网 > 在精选推荐里,直接显示找到【云耀云服务器L实例】或者直接在搜索该产品。

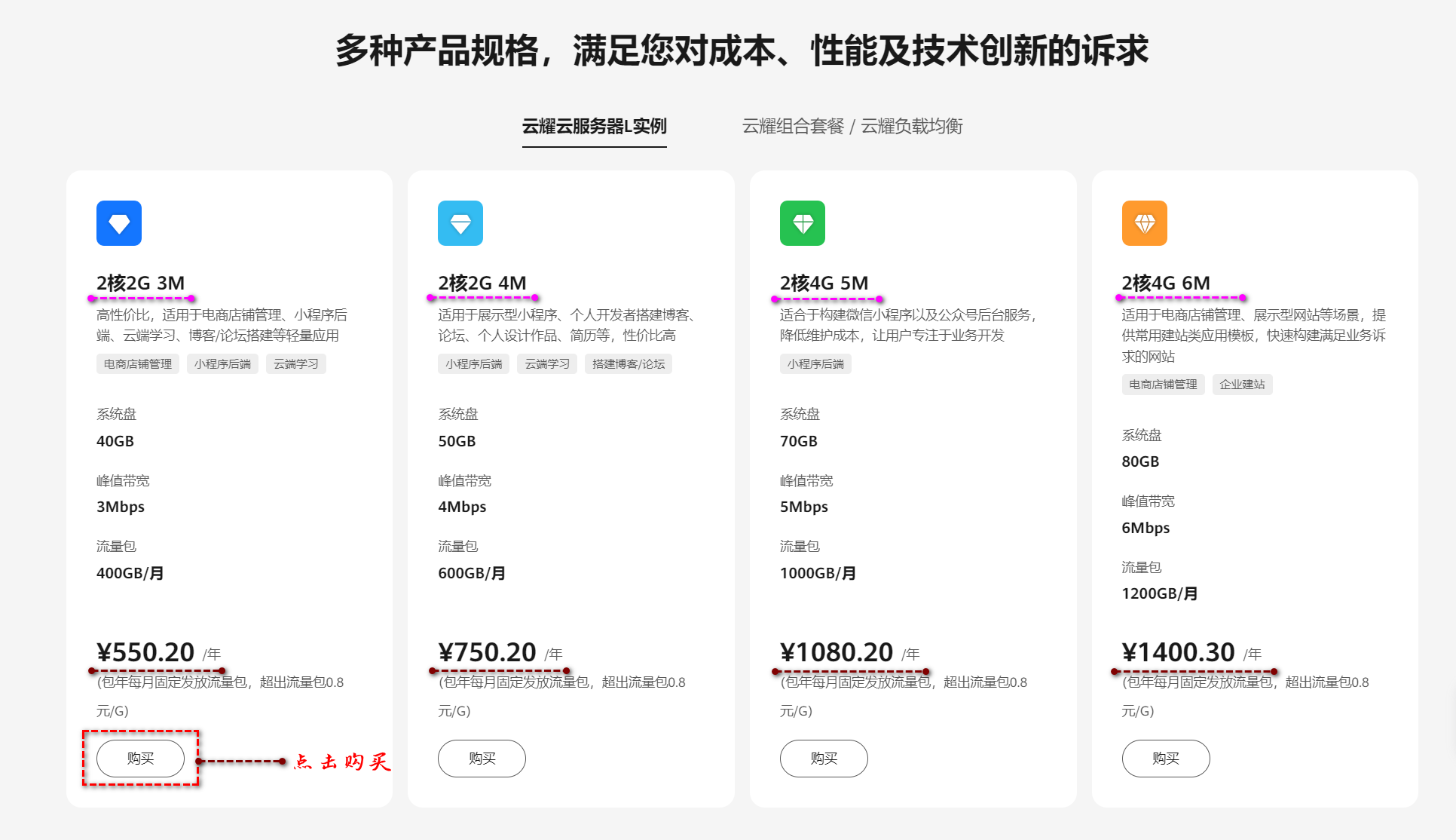

进入到云耀云服务器L实例页面后,直接点击【购买】按钮,或者点击下面的选择规格在购买

在选择规格购买页面可以看到,默认的推荐的4个规格,其中包括 CPU、内存、硬盘和带宽规格等,规格越高,价格也会越高,适用的场景也会不同,对于自身具体选择哪一个,可以根据自身的应用场景与预算适当选择。

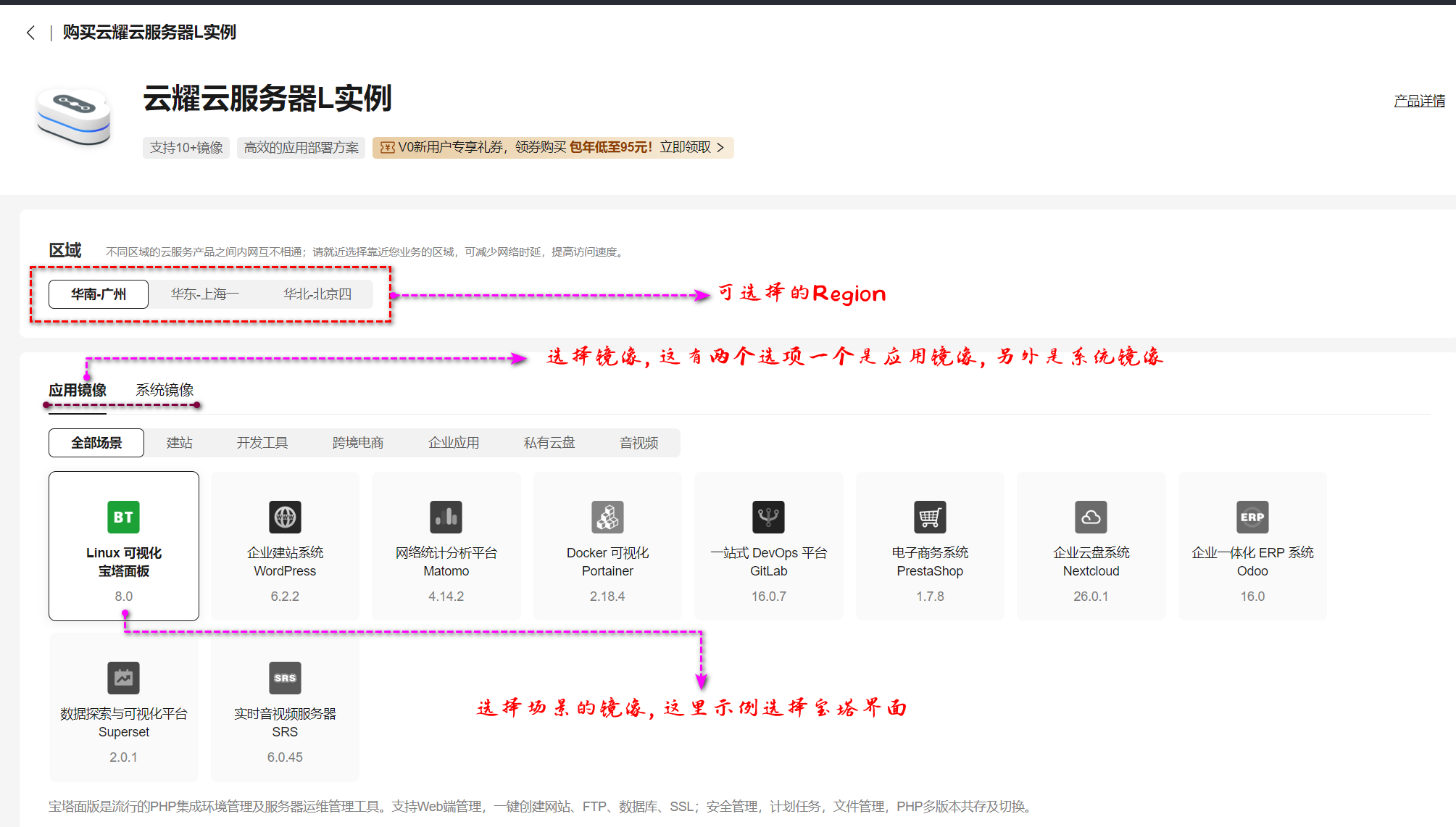

在点击购买按钮后,会出现下面云耀云服务器L实例所在区域(Region)和镜像选择页面。

在区域内,现时点可以看到有推荐的3个区域:

- 华南-广州

- 华东-上海

- 华北-北京四

在选择镜像方面,如我上述在【2.4 云耀云服务器L实例支持的镜像与应用场景】节介绍的一样,有应用镜像与系统镜像可选。

我们这里为了演示选择“Linux 可视化宝塔面板”镜像

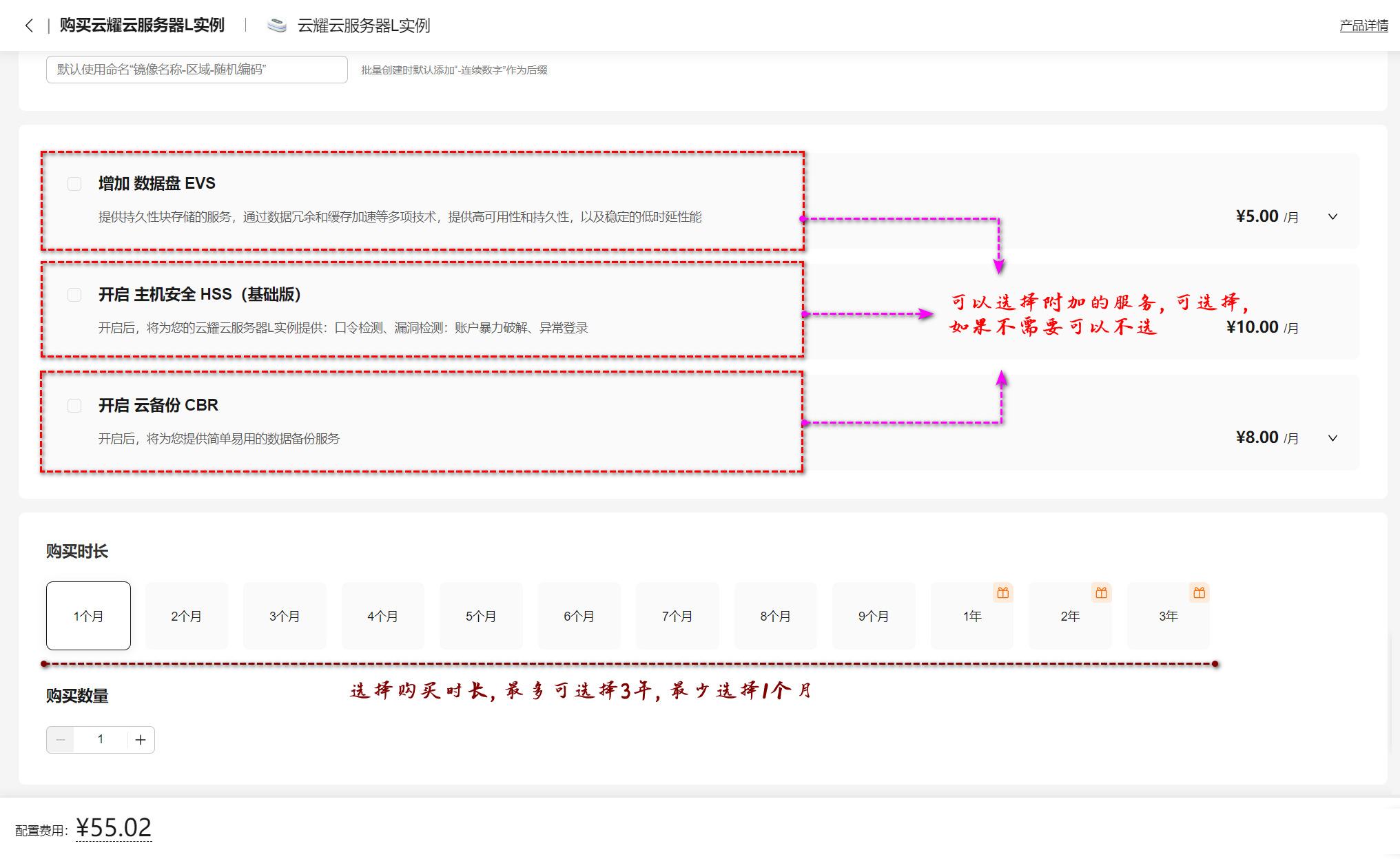

接下来可以配置一些附加功能,比如增加云硬盘,或者云备份等服务,可以根据自身所需选择是否增加服务

选择购买时长,最多可选择3年,最少选择1个月

最后确认详细信息无误以后,进行购买与支付。

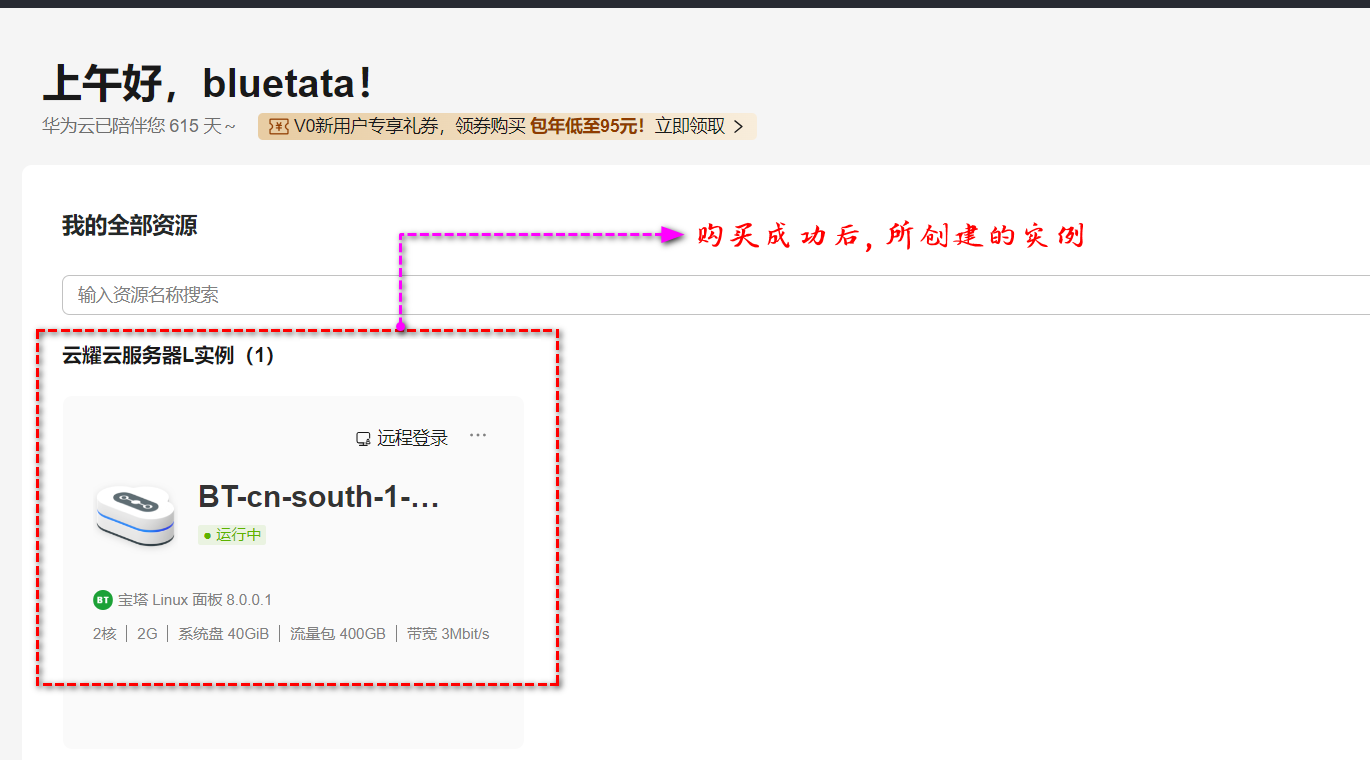

支付成功后,在控制台可以看到所购买的华为云云耀云服务器 L 实例,如下图所示:

四、宝塔应用搭建

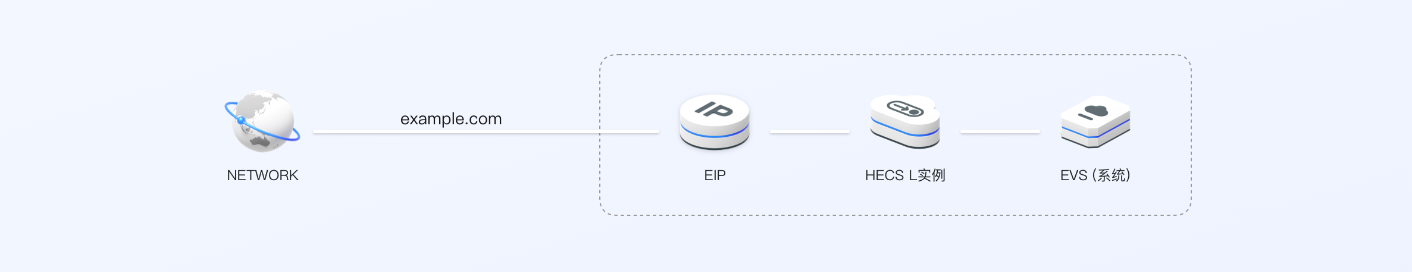

4.1 资源概览

我们从下图可以看到所购买的华为云云耀云服务器L实例的资源概览

其中包括 EIP 的公网ip,HECS L 实例,以及云硬盘 EVS。

4.2 宝塔应用搭建

我们在控制台的时候可以看到应用搭建的模块,值得一提的是,从初始化环境到搭建应用非常简单,就两个步骤:

- 设置服务器密码

- 配置安全组

完成上述两个步骤即可直接体验开箱即用的华为云云耀云服务器L实例

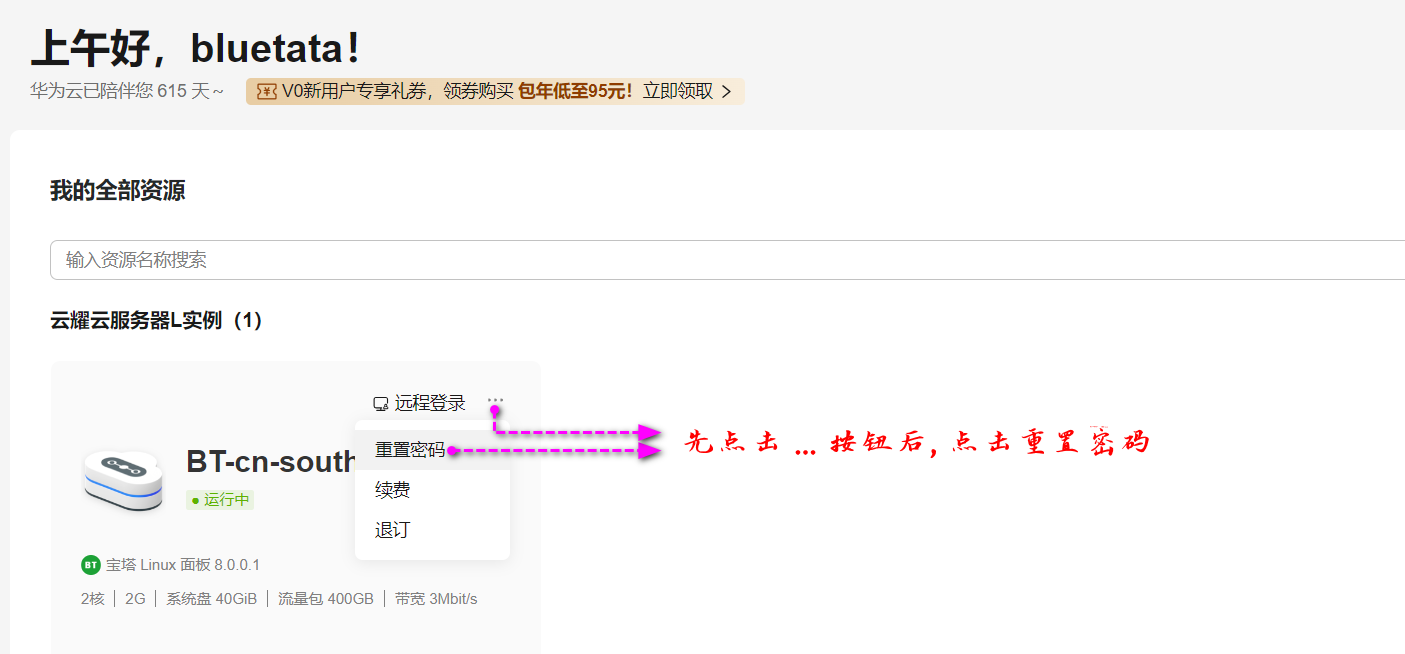

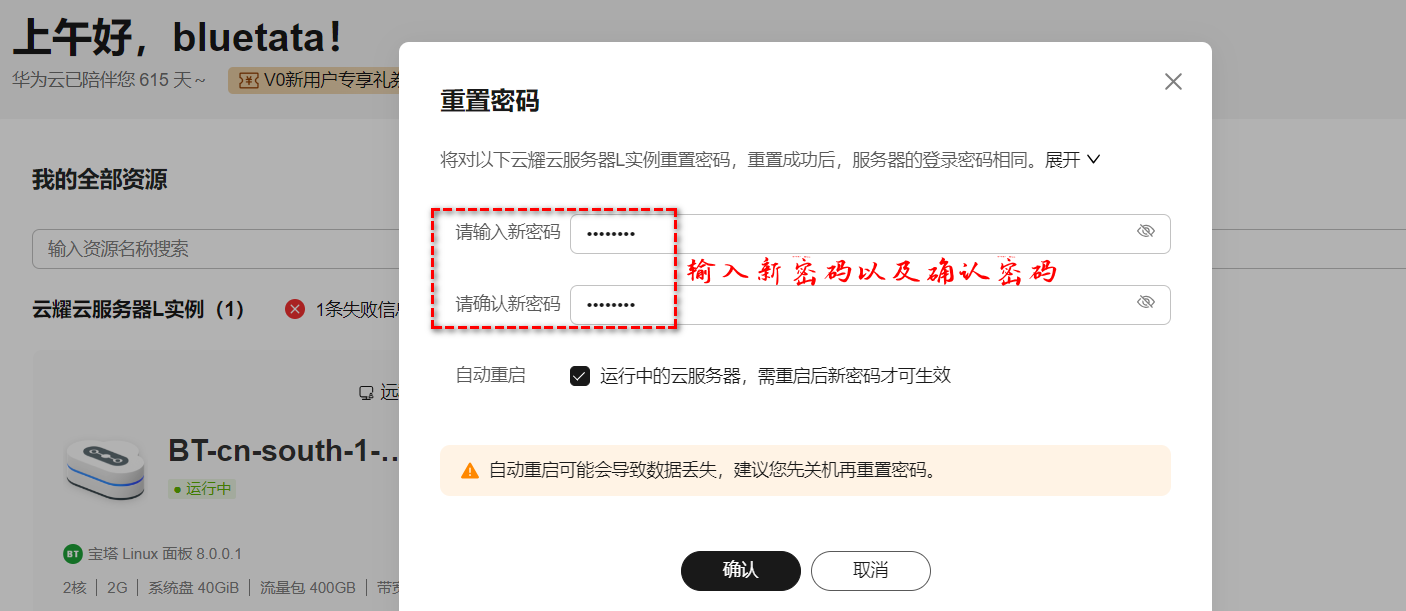

4.2.1 重置密码

先点击...按钮后,点击重置密码。

重置密码的页面内输入新密码以及确认密码

在重置密码的页面中有默认的勾选选项,运行中的云服务器需要重启后新密码生效,

所以如果你的服务器正在运行中,并且你需要改密码,如果不影响业务的时候,可以直接勾选重启,如果需要自定义时间重启,那么你需要取消掉这个勾选项才可以。

注意:如果出现如下提示,那么证明敏感操作需要身份验证,你需要去远程登录页面去修改密码。

已开启操作保护,进行敏感操作需要进行身份验证。

建议:点击“远程登录”,在该页面右侧操作区“重置密码”。

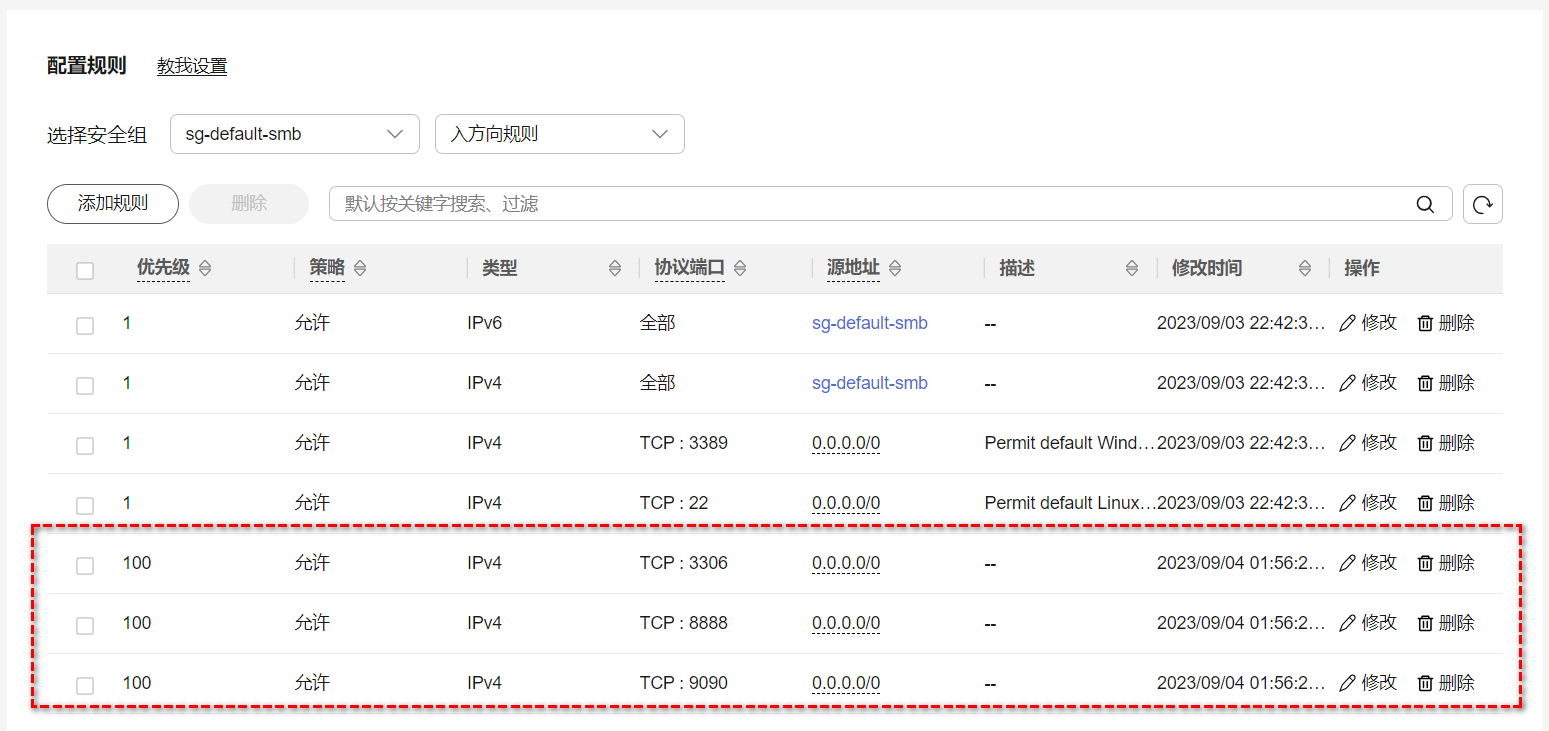

4.2.2 配置安全组

进入云耀云服务器L实例控制台,单击云耀云服务器L实例卡片,进入资源页面。

在左侧列表中单击“云耀云服务器L实例”,单击云服务器名称,进入云服务器详情页面。

选择“安全组”页签,单击“添加规则”,根据自身的服务,可以添加如下规则配置。

| 优先级 | 策略 | 类型 | 协议端口 | 源地址 | 描述 |

|---|---|---|---|---|---|

| 100 | 允许 | IPv4 | TCP:8888 | 0.0.0.0/0 | 允许访问宝塔面板。 |

| 100 | 允许 | IPv4 | TCP:3306 | 0.0.0.0/0 | 允许访问MySQL数据库。 |

| 100 | 允许 | IPv4 | TCP:9090 | 0.0.0.0/0 | 允许访问phpMyAdmin数据库管理工具。 |

| 100 | 允许 | IPv4 | TCP:443 | 0.0.0.0/0 | 允许使用HTTPS协议访问应用管理界面。 |

| 100 | 允许 | IPv4 | TCP:80 | 0.0.0.0/0 | 允许使用HTTP协议访问应用管理界面。 |

如下图所示,进入安全组 页签内。

需要配置安全组的入方向访问规则,确保可以正常访问。

访问应用需开通8888端口、访问 phpMyAdmin 数据库需开通9090端口、访问 MySQL 数据库需开通3306端口。

直接添加如下所示的入站规则:

添加完入站规则后,如下图所示:

设置完上述的所有步骤后,接下来就可直接登录宝塔控制页面了。

4.2.3 验证登录宝塔页面

经过上述配置的几个步骤后,已经完成了宝塔的安装,可以看出在使用华为云云耀云服务器L实例中选择应用镜像的时候,开箱即用服务非常简单方便。

(1)访问并登陆宝塔

宝塔默认地址为:http://弹性ip:8888/login,如果配置的安全组没有问题,直接访问宝塔链接后,显示如下图所示登陆页面。

第一次访问宝塔页面正常会出现登陆用户名密码,访问成功后会出现宝塔控制台页面,如下图所示:

如果第一次没有看到用户名与密码,可以使用SSH进行链接到华为云云耀云服务器L实例,之后按照如下的步骤查看或者修改默认用户名与密码。

(2)查看宝塔默认密码

执行下面的命令进行查看宝塔默认的登陆账号和密码:

sudo cat /credentials/password.txt

root@hcss-ecs-f3d5:~# sudo cat /credentials/password.txt

========= credentials for bt =========

bt_user: administrator

bt_password: 5BkR6CMBRw8GSJ!(3)修改宝塔默认密码

执行下面命令进行修改宝塔的默认账号密码:

bt 5

root@hcss-ecs-f3d5:~# bt 5

===============================================

正在执行(5)...

===============================================

请输入新的面板密码:P@ssw0rd

|-用户名: administrator

|-新密码: P@ssw0rd

五、文末总结

在本文中,我们详细介绍了云耀云服务器L实例的产品定位和优势,以及与弹性云服务器(ECS)的区别。我们还讨论了如何购买和配置云耀云服务器L实例,并展示了如何使用宝塔进行应用搭建、重置密码、配置安全组以及验证登录宝塔页面等操作。

通过本文,您应该对云耀云服务器L实例有了更清晰的了解,并掌握了使用宝塔进行应用管理的基本步骤。无论您是初次使用云服务器还是已经有一定经验,本文都希望能够帮助您更好地利用云耀云服务器L实例来满足您的需求,实现更高效的云端应用部署和管理。