网站内容编辑工具中国工业信息网

背景介绍

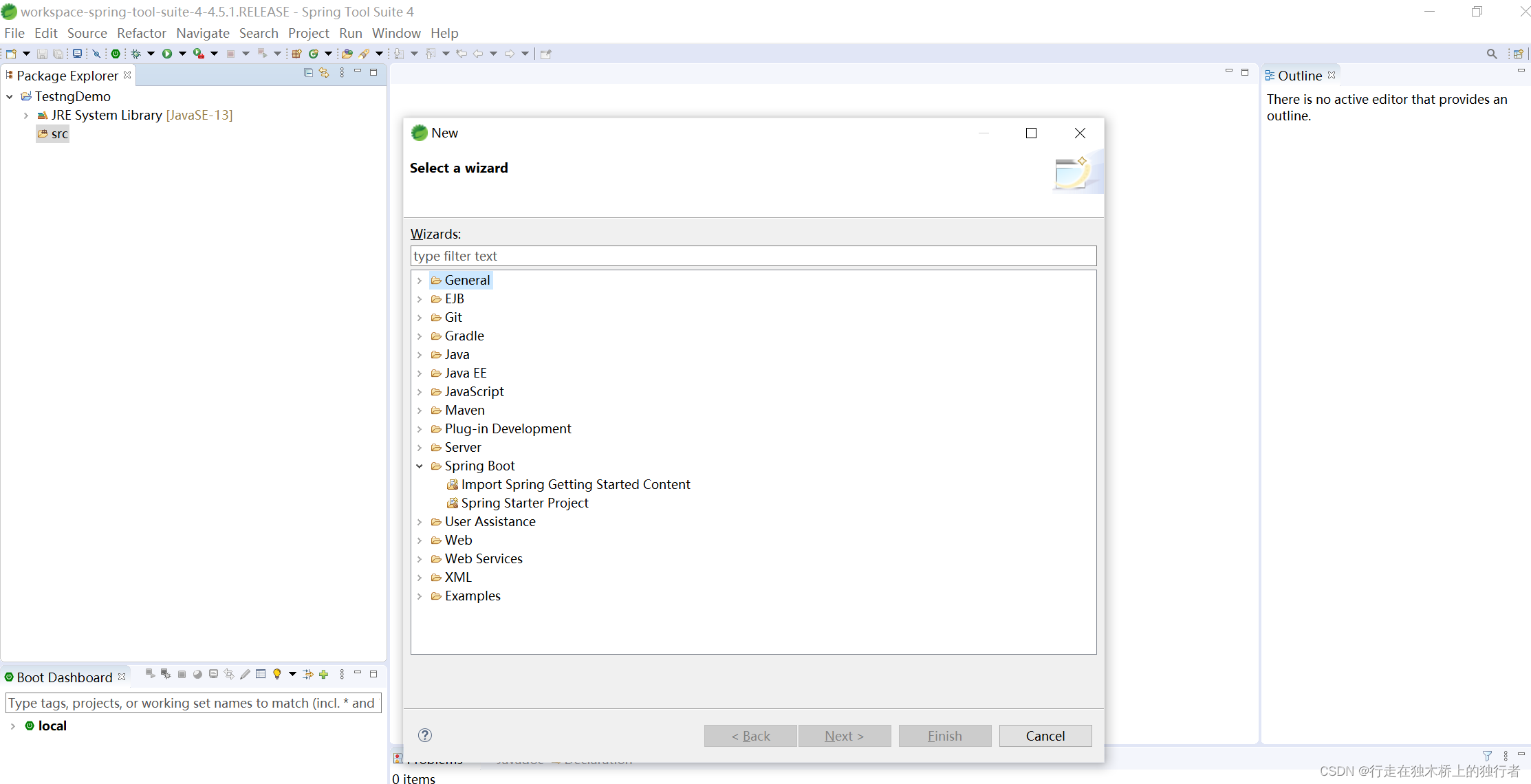

在创建spring项目后,如果想想创建spring bean Configuration的时候,发下菜单没有这个选项,需要通过下载Spring Roo插件可满足该操作。

参考案例

参考地址:

STS4 New 菜单没有Spring Bean Configuration File选项_SQZHAO的博客-CSDN博客

下载插件

Spring Roo下载地址:

https://projects.spring.io/spring-roo/#download-widget

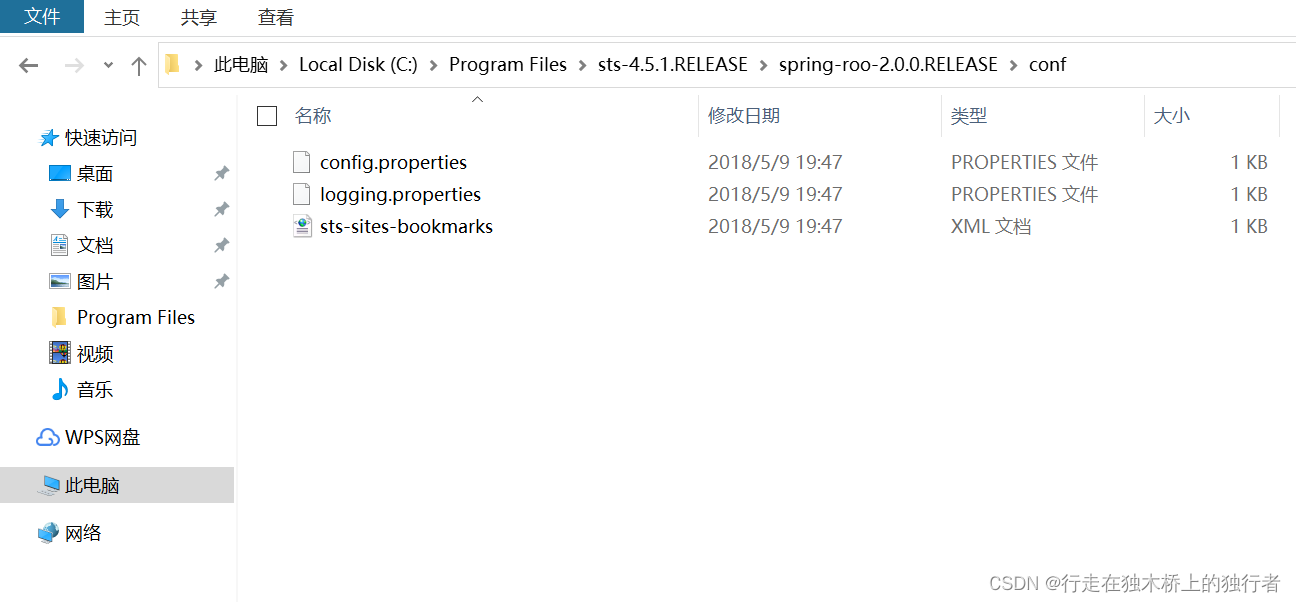

导入插件配置文件

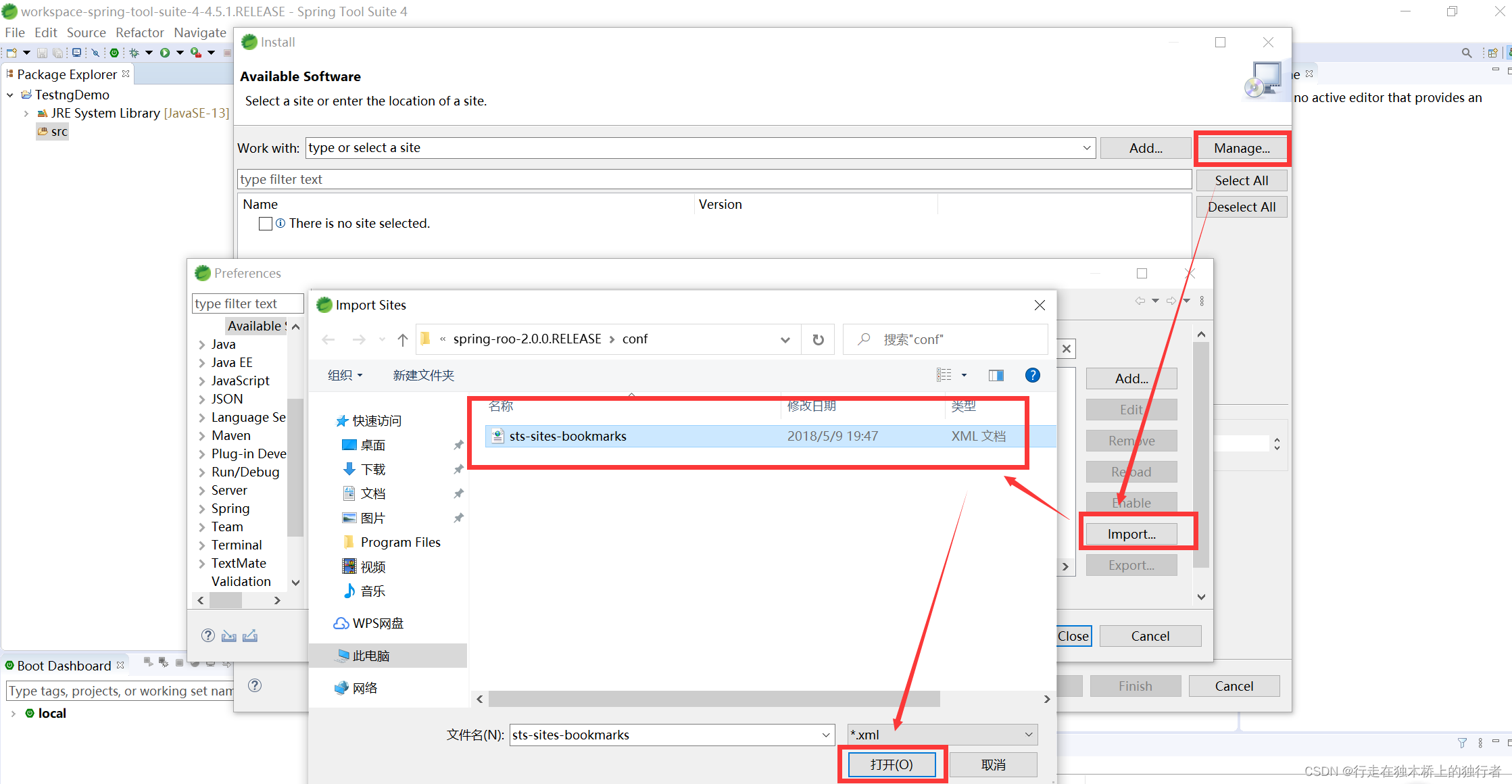

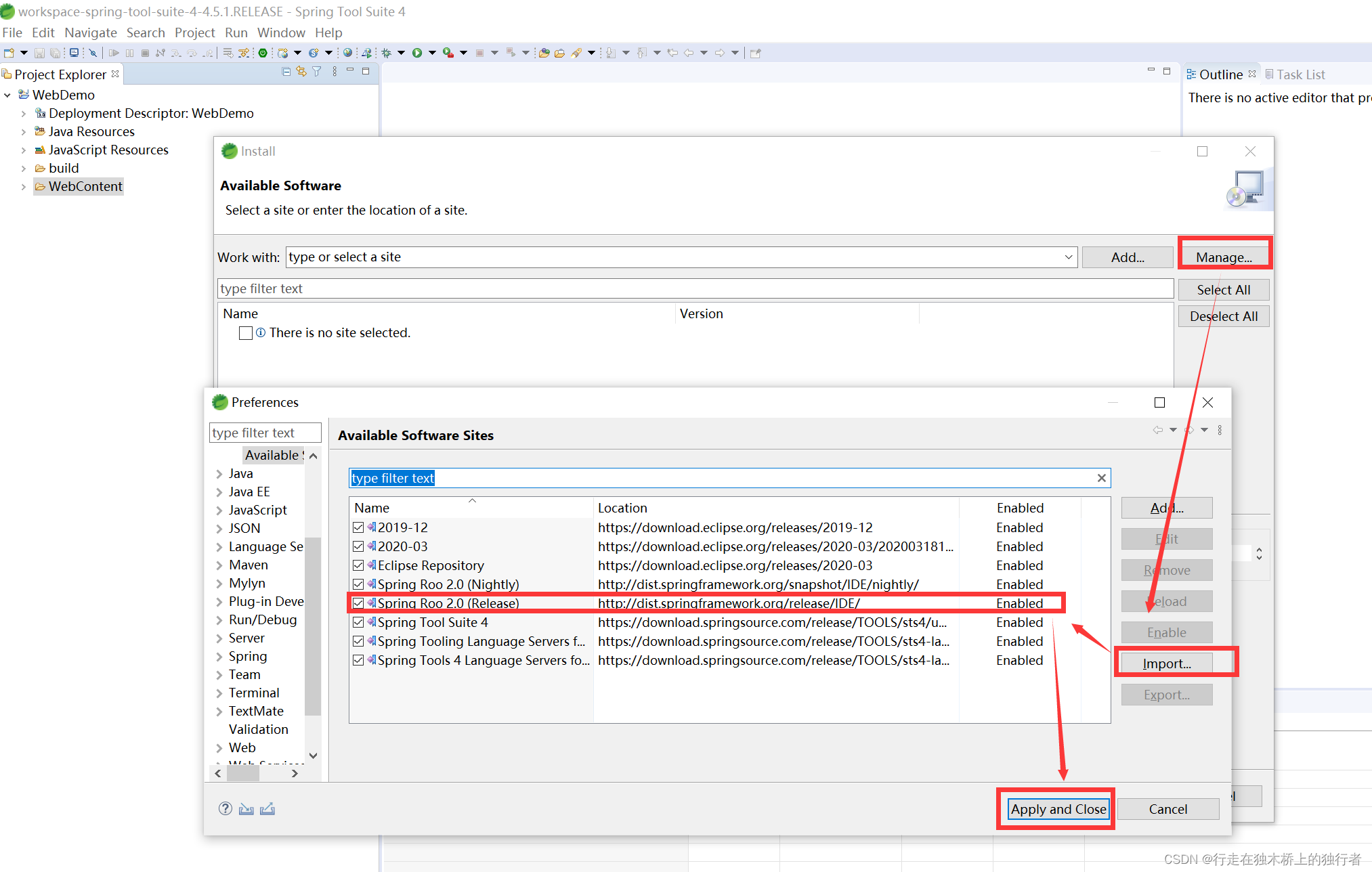

解压spring roo后,打开STS4,Help -> Install New Software->Manage -> Import按钮,选择解压后的spring roo/config下的xml文件

点击Applyand Close按钮,完成添加。

在Work with中选择添加的xml文件的配置路径http://dist.springframework.org/release/IDE/

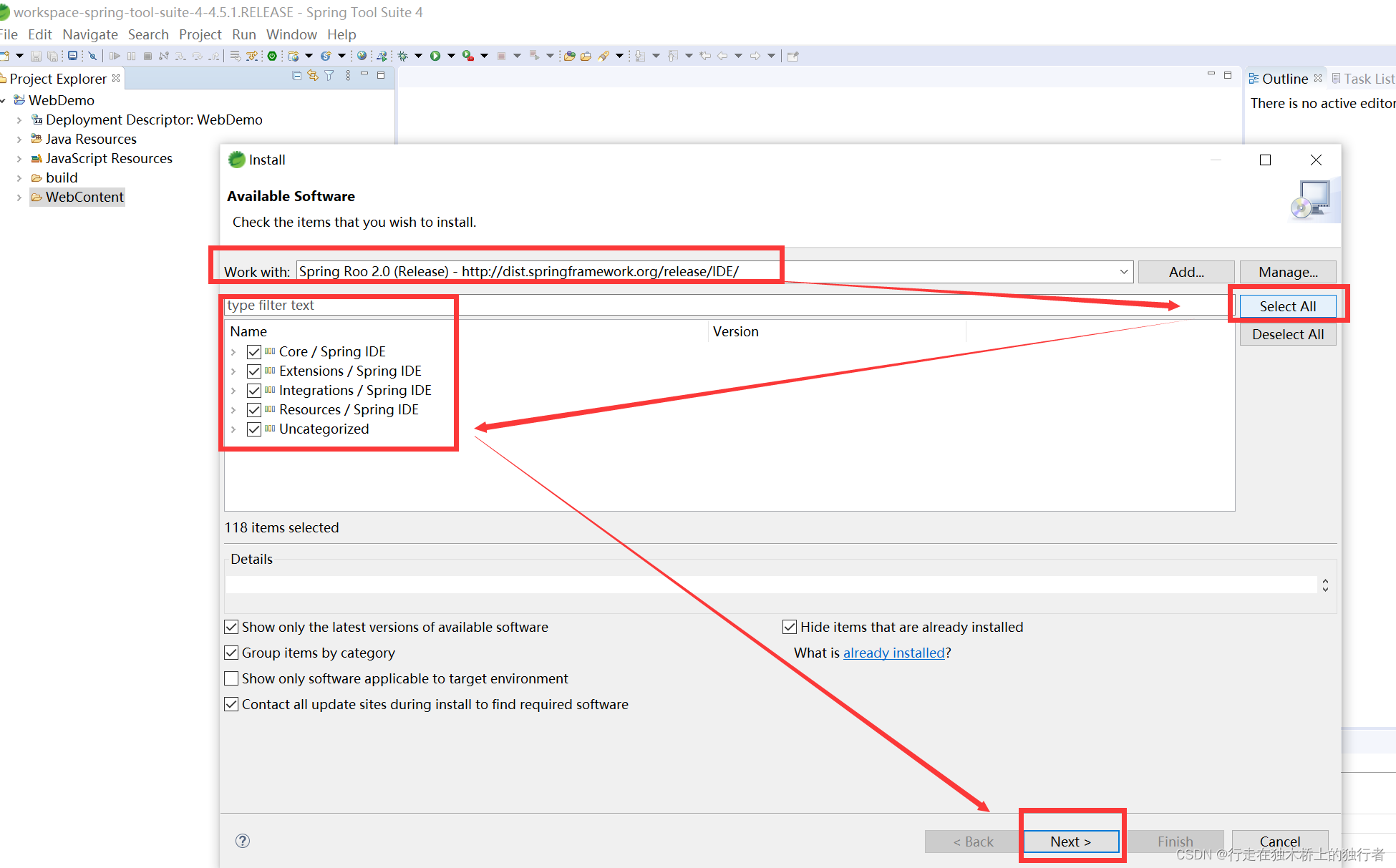

选择Select All->Next按钮,计算需要安装和依赖的文件。

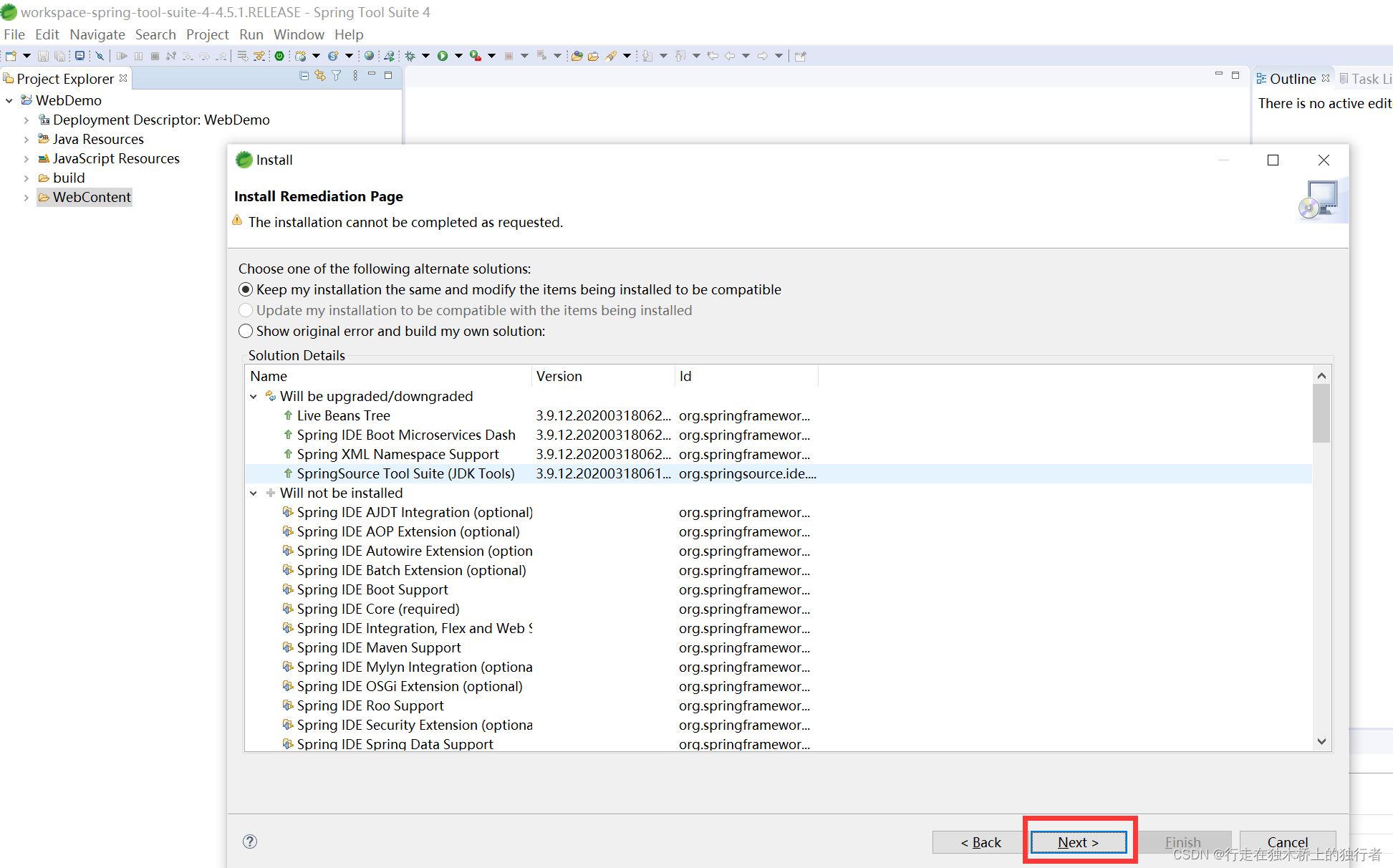

点击Next按钮

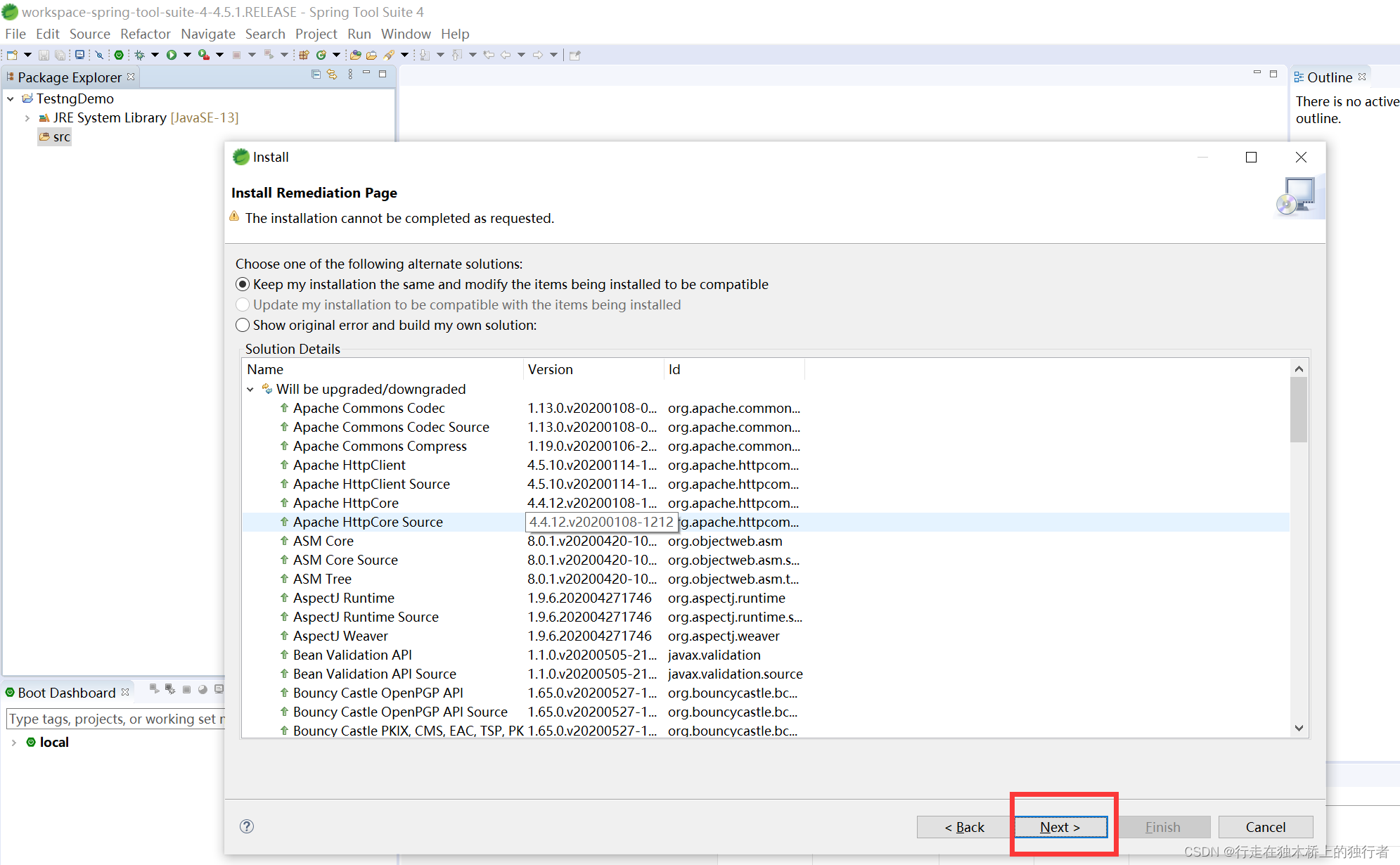

点击Next进行按钮。

点击Next按钮

点击Finish按钮,完成安装

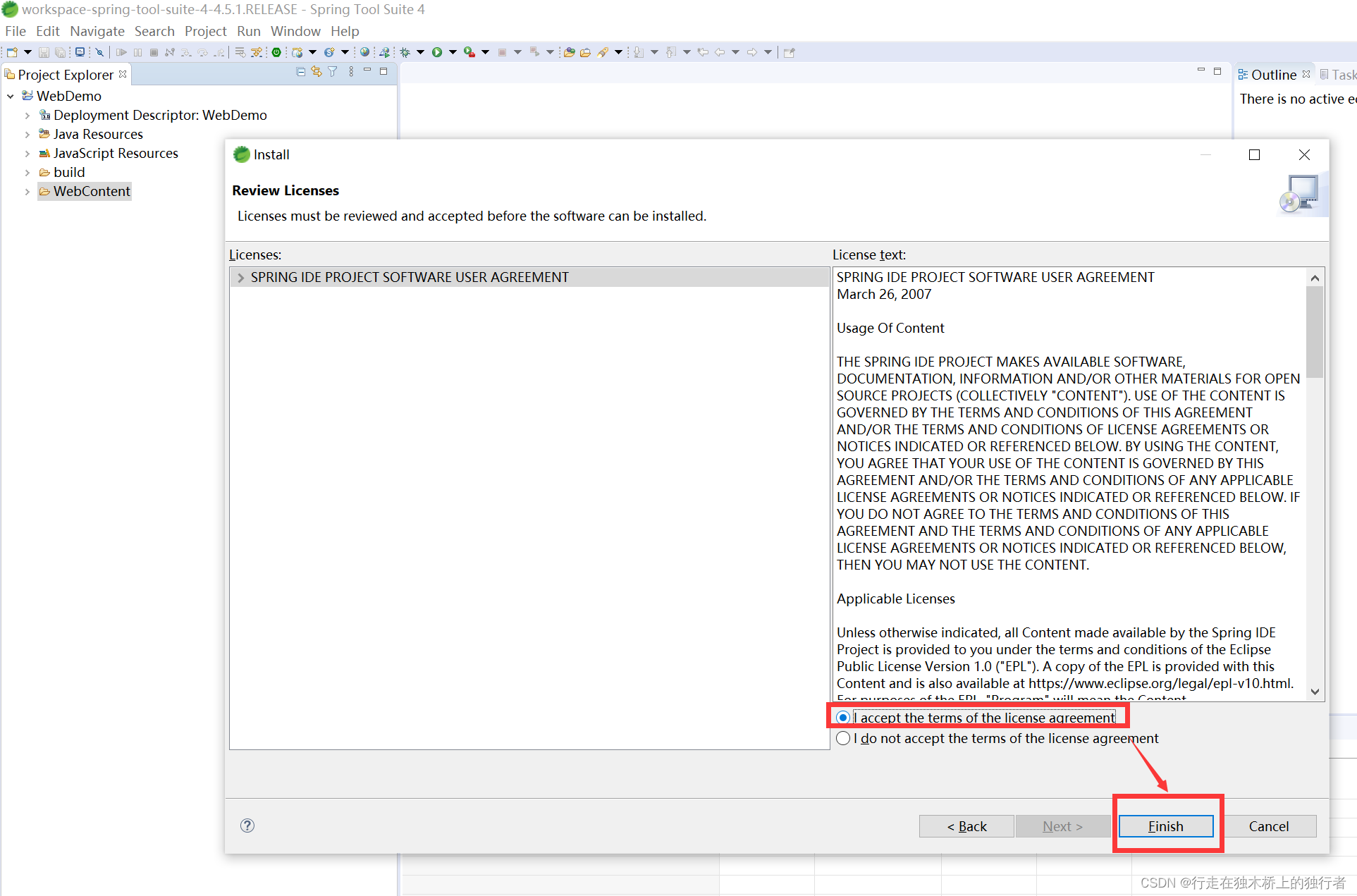

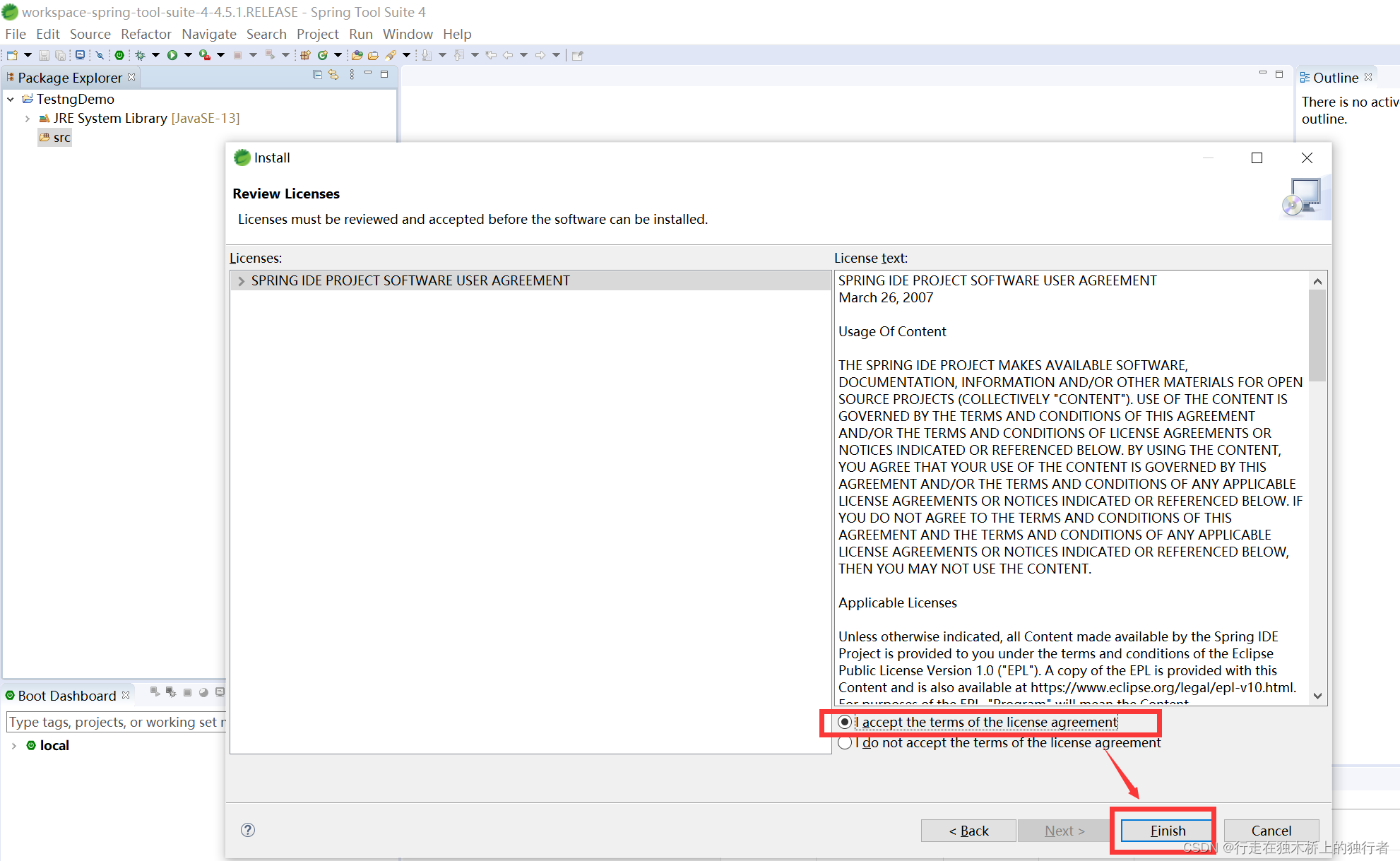

选择接受协议,点击Finish按钮,进行安装。

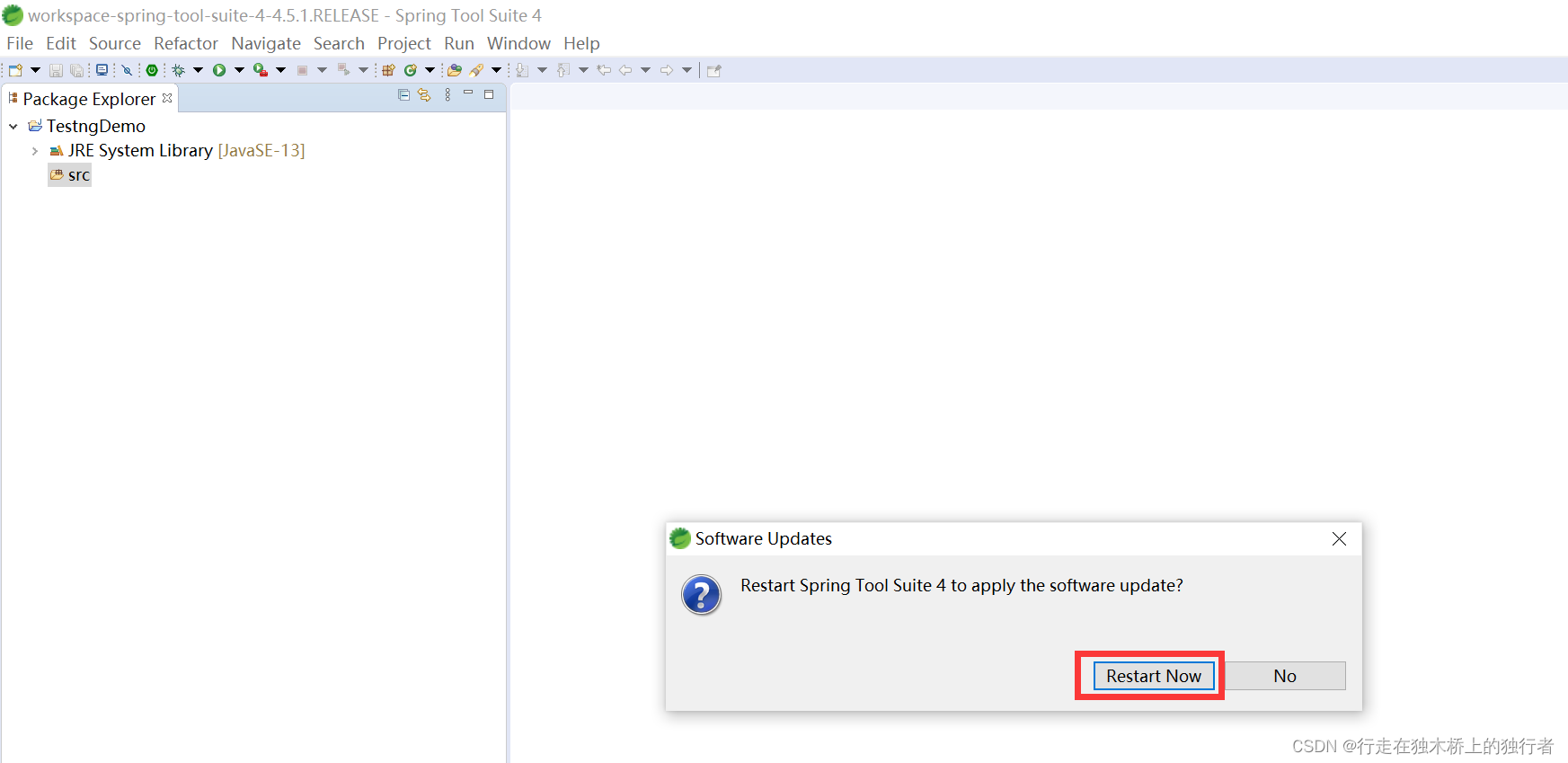

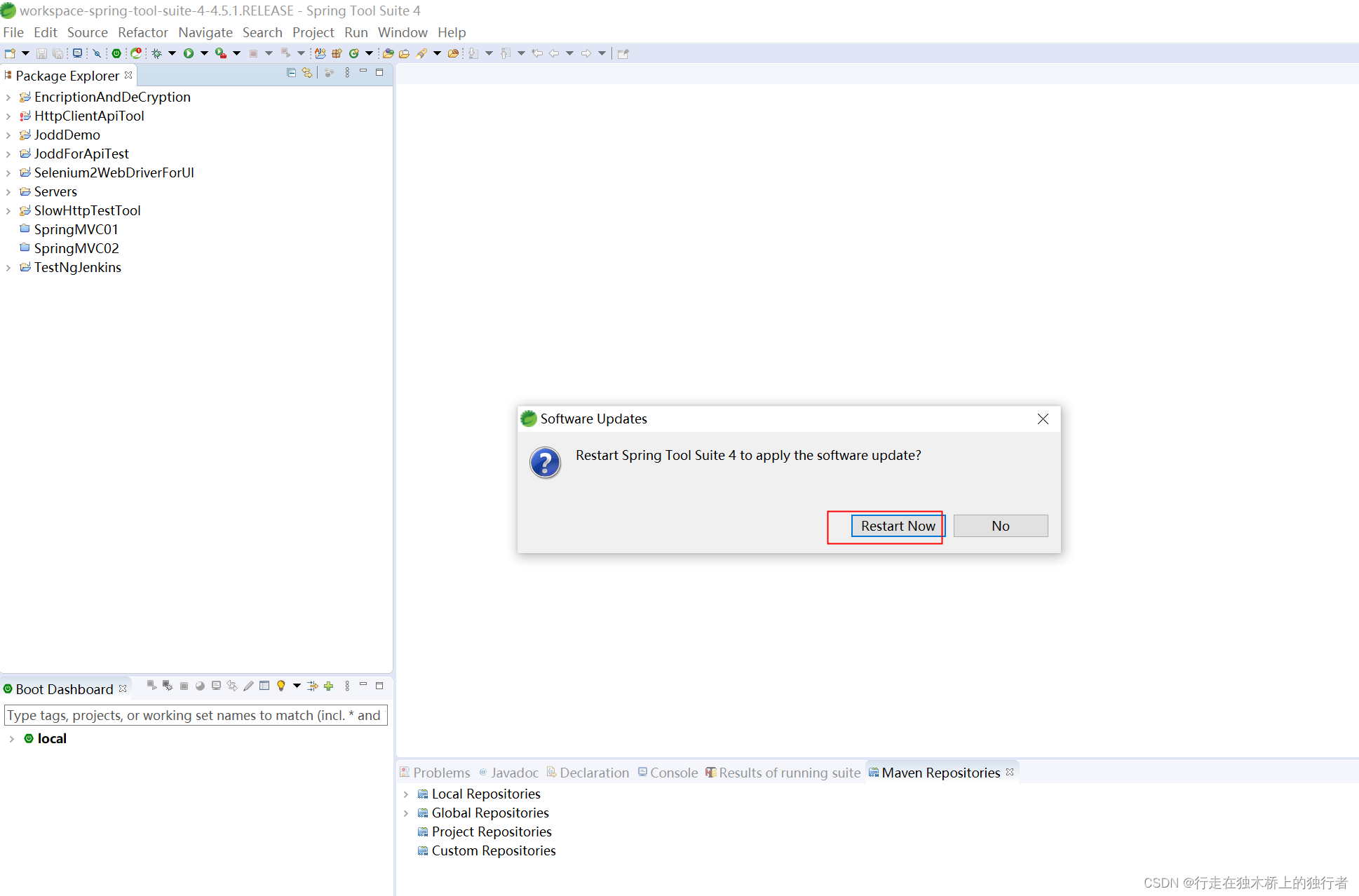

下载完成后,点击Restart Now按钮重启。

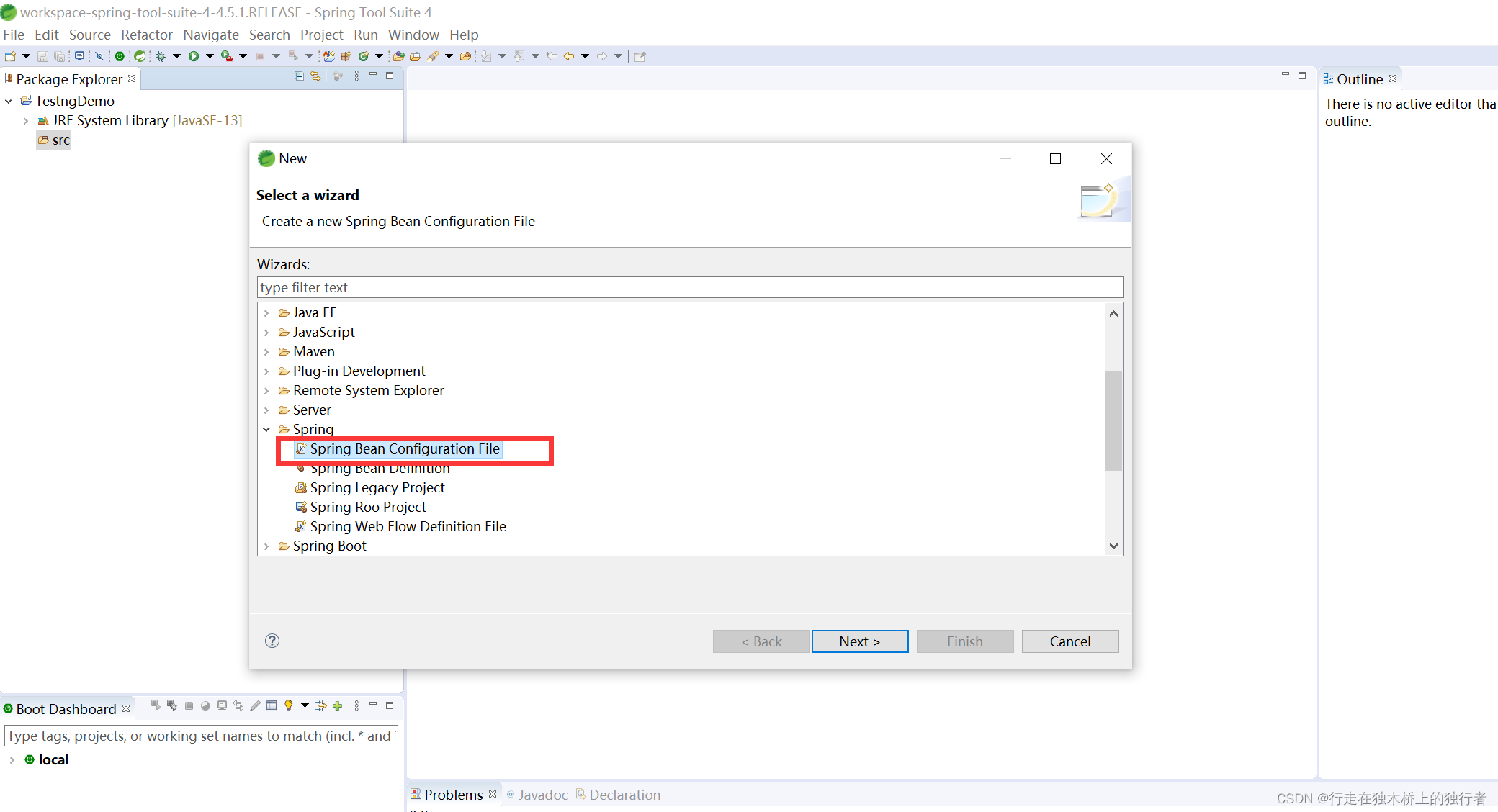

安装成功后,新建-other-spring选项中可以看到Spring Bean Configuration菜单。

安装Maven

官方参考资料

M2Eclipse | M2EclipseM2Eclipse provides tight integration for Apache Maven into the Eclipse IDE.![]() https://www.eclipse.org/m2e/

https://www.eclipse.org/m2e/

Project download area | The Eclipse FoundationThe Eclipse Foundation - home to a global community, the Eclipse IDE, Jakarta EE and over 360 open source projects, including runtimes, tools and frameworks.![]() http://download.eclipse.org/technology/m2e/releases/

http://download.eclipse.org/technology/m2e/releases/

安装配置过程

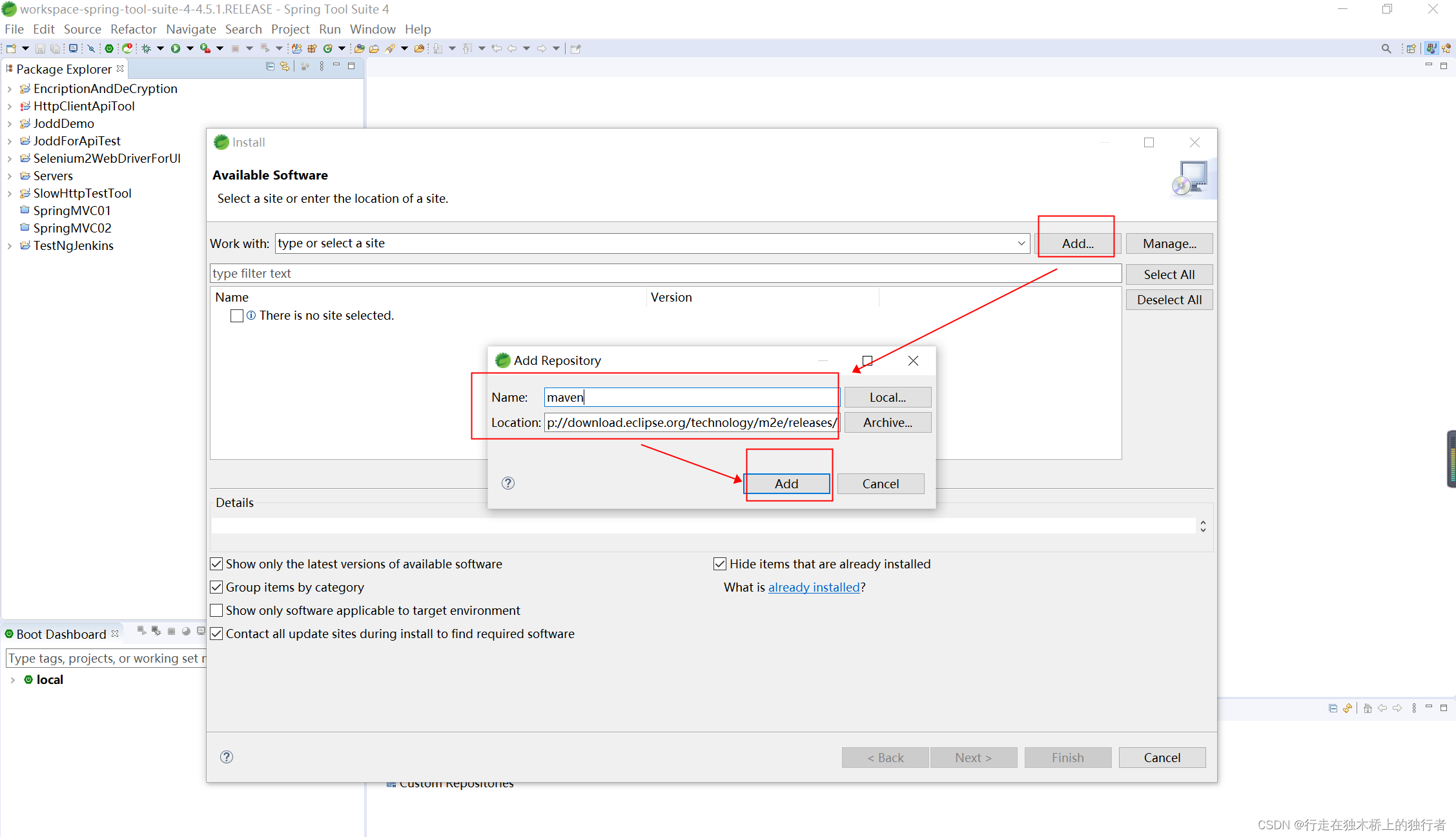

点击工具的菜单栏,help->Install New Software,打开Avaliable Software窗口,然后点击Add按钮,输入maven的url和名字后,点击Add按钮。

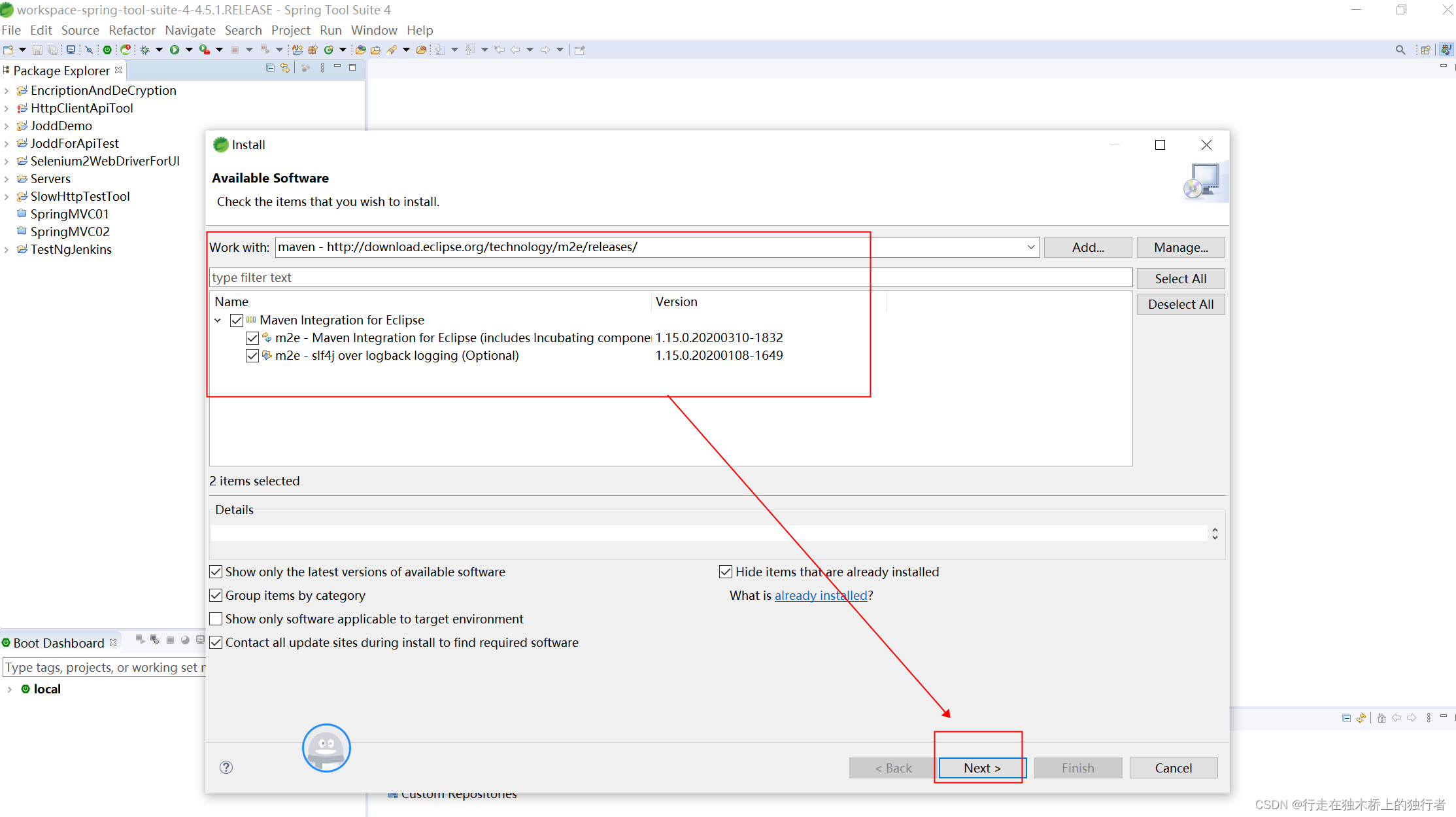

加载出下载地址后,选择加载的内容,然后地单机Next按钮。

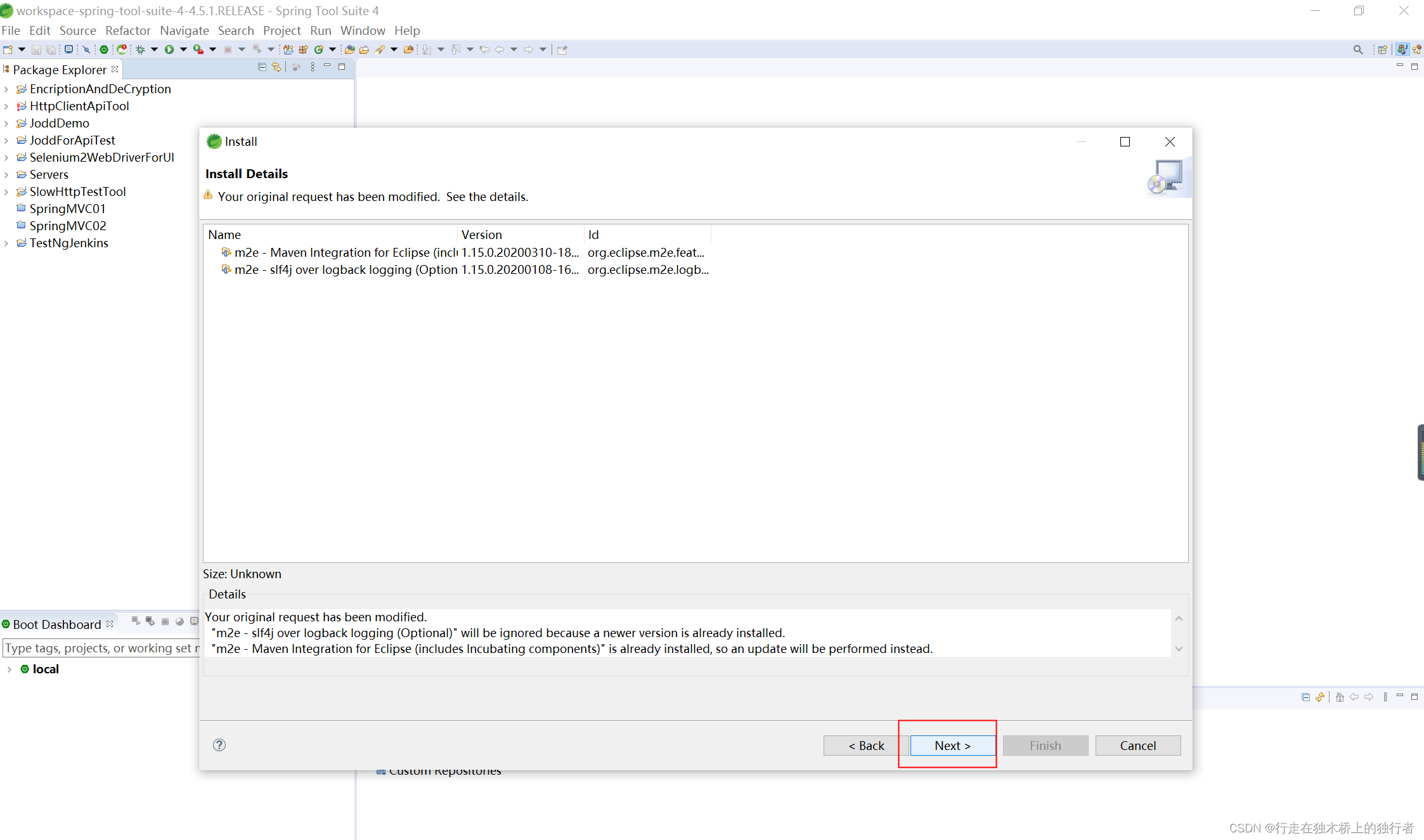

点击Next按钮。

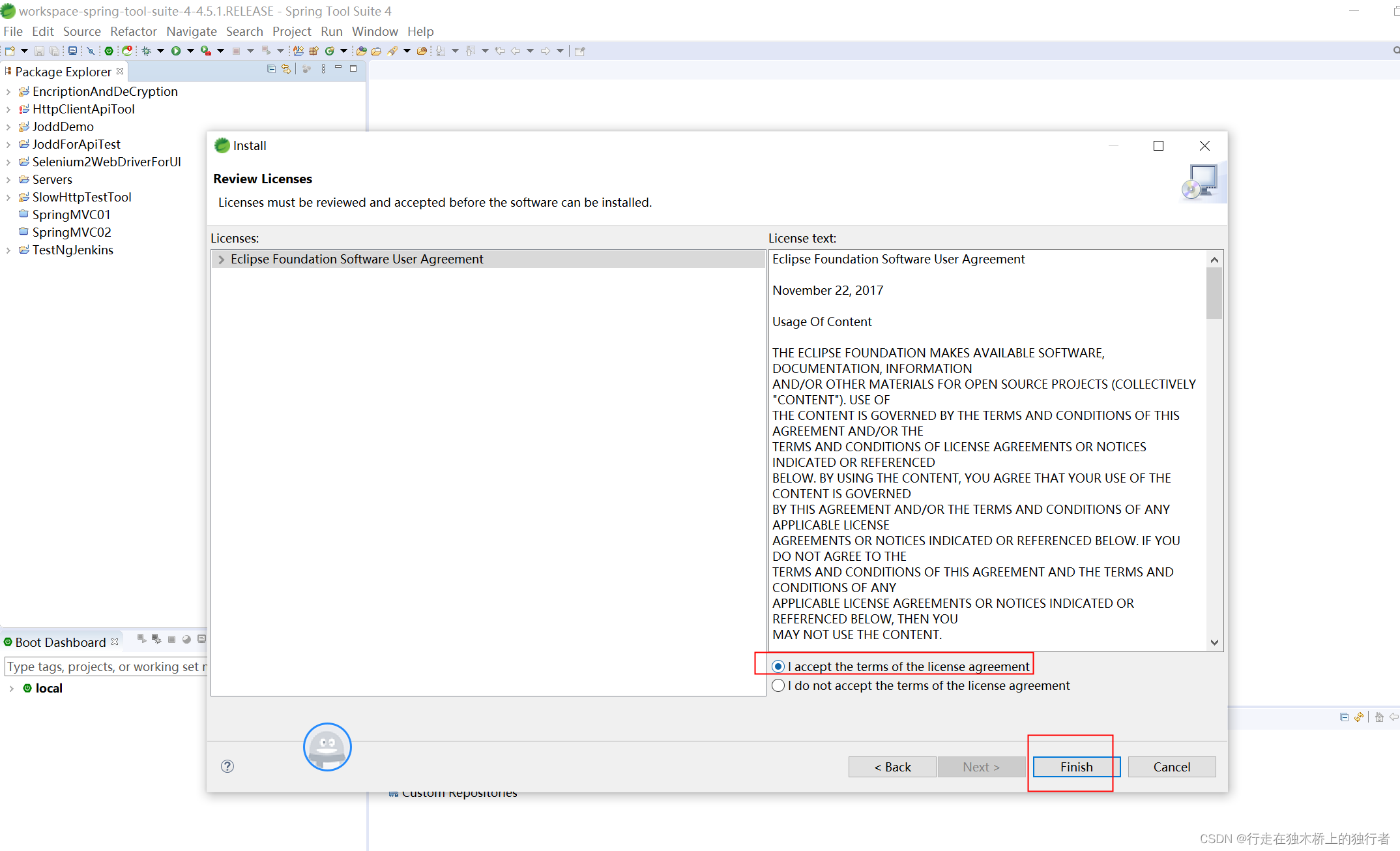

勾选接受协议,然后点击Next按钮。

安装成功后,点击Restart Now按钮重启工具,安装生效