免费舆情网站下载大全最新版网站建设服务面试题

Citrix在数据库的连接方式上一直不统一,但是也还是有迹可循的。

经过了好长时间的下载以后,今天终于有时间来测试一下最新版本的XenDesktop 5 SP1,由于结合了其他组件和环境的需要,所以,选择了独立部署数据库,使用了SQL SERVER 2008 R2企业版,而不是XenDesktop 5 自带的SQL EXPRESS。

安装过程非常顺利,创建Site的时候,问题就来了。一直无法通过连接测试,提示我检查数据库的远程访问设置、权限和防火墙设置。

The Database server may not be allowing remote connections,make sure the database server is setup correctly and that the firewall is not blocking the connections.

经过排查直接忽略了这些问题,因为我另外一台XenApp服务器已经顺利安装通过。

后来经过查找,发现,是server location的设置问题,不得不说是件很郁闷的事情:

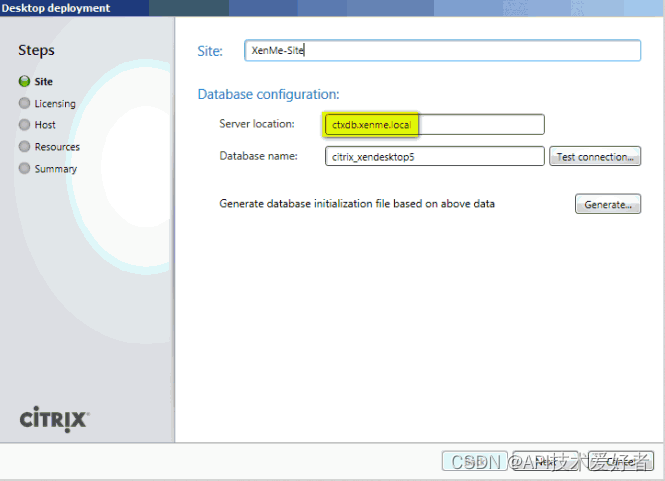

如图,这里需要填写ctxdb.xenme.local,而不是ctxdb\mssqlserver等等。

由于XenDesktop的一些设置,这里的填写方式有些特别,作如下总结:

- 如果是本地数据库,不管是否是express版本,不能使用.和localhost之外的主机名等等,后面可以跟实例名。

- 如果是外部数据库,那么server location就只能填写FQDN,hostname,IP Address,但后面不能跟实例名。

说明:外部使用express版本数据库或者非默认实例名(mssqlserver)数据库的连接,可以尝试以上组合。这里就不去测试了。

关于XenDesktop 5 数据库的权限问题,我会再开一篇文章专门来说明一下,解决大家的一些疑惑。