源码网站违法吗肥东建设网站

一.AOP切面公共字段填充

问题分析

如果都按照上述的操作方式来处理这些公共字段, 需要在每一个业务方法中进行操作, 编码相对冗余、繁琐,那能不能对于这些公共字段在某个地方统一处理,来简化开发呢?

答案是可以的,我们使用AOP切面编程,实现功能增强,来完成公共字段自动填充功能。

实现思路

1. 2 在发生insert操作时 需要为字段赋值

3. 4 在发生insert update操作时 需要为字段赋值

我们为了简便操作就要通过切面这种方式统一处理为这几个字段赋值的操作

比如在持久层Mapper 执行insert, 就可以通过切面拦截这个insert操作

我们还需要设置一个手段, 能够知道当前持久层的操作是否需要为公共字段赋值(一堆连接点怎么找切入点)

我们就是通过 自定义注解 的方式为这个Mapper的方法加入注解, (让这个方法成为切入点)

作为一个标识表示该操作需要赋值 没有标识就不需要

整体实现过程:

技术点:枚举、注解、AOP、反射

1) 枚举(创建一个枚举类, 包含insert, update, 加在注解类AutoFill内部,用以区分是需要为四个字段还是两个字段赋值)

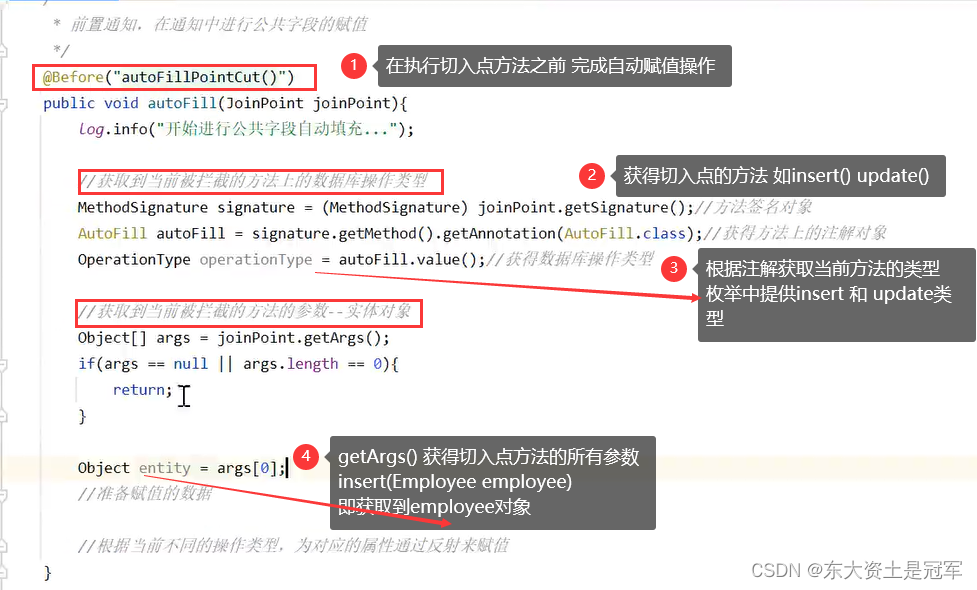

2). 自定义注解 AutoFill,用于标识需要进行公共字段自动填充的方法

3). 自定义切面类 AutoFillAspect,统一拦截加入了 AutoFill 注解的方法,通过反射为公共字段赋值

在内部使用反射机制完成赋值

//根据当前不同的操作类型,为对应的属性通过反射来赋值if(operationType == OperationType.INSERT){//为4个公共字段赋值try {Method setCreateTime = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_CREATE_TIME, LocalDateTime.class);Method setCreateUser = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_CREATE_USER, Long.class);Method setUpdateTime = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_UPDATE_TIME, LocalDateTime.class);Method setUpdateUser = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_UPDATE_USER, Long.class);//通过反射为对象属性赋值setCreateTime.invoke(entity,now);setCreateUser.invoke(entity,currentId);setUpdateTime.invoke(entity,now);setUpdateUser.invoke(entity,currentId);} catch (Exception e) {e.printStackTrace();}}else if(operationType == OperationType.UPDATE){//为2个公共字段赋值try {Method setUpdateTime = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_UPDATE_TIME, LocalDateTime.class);Method setUpdateUser = entity.getClass().getDeclaredMethod(AutoFillConstant.SET_UPDATE_USER, Long.class);//通过反射为对象属性赋值setUpdateTime.invoke(entity,now);setUpdateUser.invoke(entity,currentId);} catch (Exception e) {e.printStackTrace();}}4). 在 Mapper 的方法上加入 AutoFill 注解

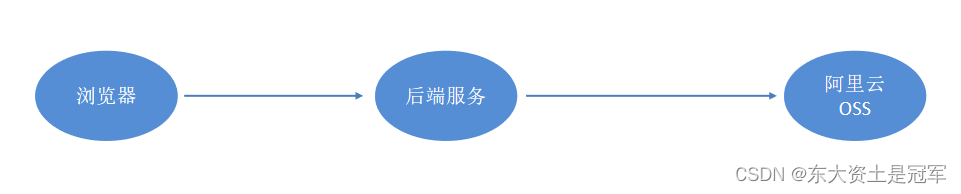

二. 阿里云文件上传

因为在新增菜品时,需要上传菜品对应的图片(文件),包括后绪其它功能也会使用到文件上传,故要实现通用的文件上传接口。

文件上传,是指将本地图片、视频、音频等文件上传到服务器上,可以供其他用户浏览或下载的过程。文件上传在项目中应用非常广泛,我们经常发抖音、发朋友圈都用到了文件上传功能。

实现文件上传服务,需要有存储的支持,那么我们的解决方案将以下几种:

- 直接将图片保存到服务的硬盘(springmvc中的文件上传)

- 优点:开发便捷,成本低

- 缺点:扩容困难

- 使用分布式文件系统进行存储

- 优点:容易实现扩容

- 缺点:开发复杂度稍大(有成熟的产品可以使用,比如:FastDFS,MinIO)

- 使用第三方的存储服务(例如OSS)

- 优点:开发简单,拥有强大功能,免维护

- 缺点:付费

在本项目选用阿里云的OSS服务进行文件存储。(前面课程已学习过阿里云OSS,不再赘述)

实现步骤:

实现步骤:

1). 定义OSS相关配置

2). 读取OSS配置

配置属性类 加载yml文件 完成赋值

3). 生成OSS工具类对象

项目启动时就可以加载下面这个配置类

启动程序 自动加载

其中AliOssUtil类

@Data

@AllArgsConstructor

@Slf4j

public class AliOssUtil {private String endpoint;private String accessKeyId;private String accessKeySecret;private String bucketName;/*** 文件上传** @param bytes* @param objectName* @return*/public String upload(byte[] bytes, String objectName) {// 创建OSSClient实例。OSS ossClient = new OSSClientBuilder().build(endpoint, accessKeyId, accessKeySecret);try {// 创建PutObject请求。ossClient.putObject(bucketName, objectName, new ByteArrayInputStream(bytes));} catch (OSSException oe) {///} catch (ClientException ce) {} finally {if (ossClient != null) {ossClient.shutdown();}}//文件访问路径规则 https://BucketName.Endpoint/ObjectNameStringBuilder stringBuilder = new StringBuilder("https://");stringBuilder.append(bucketName).append(".").append(endpoint).append("/").append(objectName);log.info("文件上传到:{}", stringBuilder.toString());return stringBuilder.toString();}

}4). 定义文件上传接口

@RestController

@RequestMapping("/admin/common")

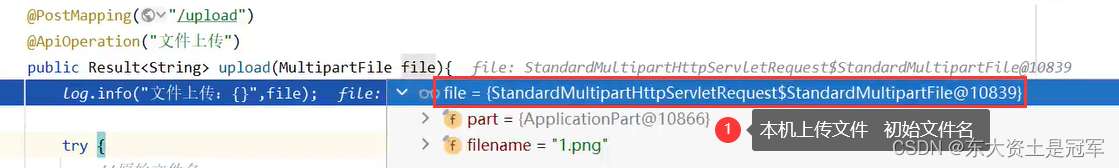

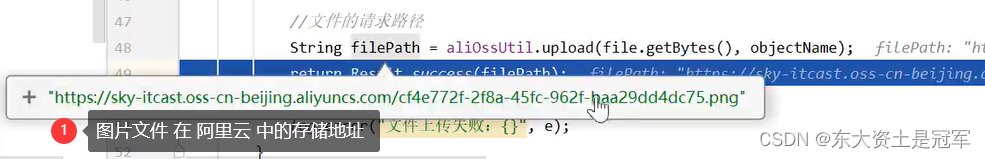

public class CommonController {@Autowiredprivate AliOssUtil aliOssUtil;/*** 文件上传*/@PostMapping("/upload")@ApiOperation("文件上传")public Result<String> upload(MultipartFile file){log.info("文件上传:{}",file);try {//原始文件名String originalFilename = file.getOriginalFilename();//截取原始文件名的后缀 dfdfdf.pngString extension = originalFilename.substring(originalFilename.lastIndexOf("."));//构造新文件名称String objectName = UUID.randomUUID().toString() + extension;//文件的请求路径String filePath = aliOssUtil.upload(file.getBytes(), objectName);return Result.success(filePath);} catch (IOException e) {log.error("文件上传失败:{}", e);}return Result.error(MessageConstant.UPLOAD_FAILED);}

}