如何诊断网站seo百度移动版

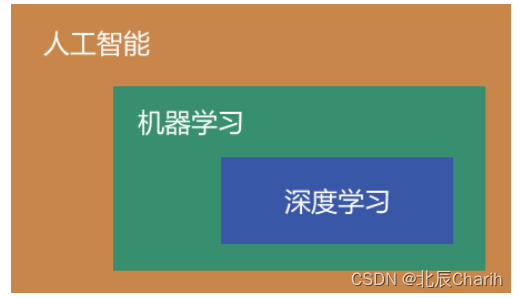

人工智能涵盖范围最广,它包含了机器学习;而机器学习是人工智能的重要研究内容,它又包含了深度学习。

人工智能(AI)

人工智能是一门以计算机科学为基础,融合了数学、神经学、心理学、控制学等多个科目的交叉学科。

人工智能是一门致力于使计算机能够模拟、模仿人类智能的学科。

它涵盖了从简单的任务执行到复杂的推理和决策等各个方面。

AI旨在开发智能代理,使其能够感知环境、学习和适应,并根据目标来采取行动。

人工智能的目的就是不给计算机编写固定的算法,而是让它自己形成一套模型,然后利用这套模型来帮助人们解决问题。这里的模型,就可以看做计算机的“经验”或者“认知”。

机器学习(ML)

机器学习是一种人工智能的分支,它关注如何通过数据和经验改进计算机系统的性能。

机器学习是一件很麻烦的事情,需要先搭建一个模型,这个模型包含了很多参数,然后把准备好的数据(包括正确的结果)输入到模型中,不断调整模型的参数,直到它非常接近或者完全符合正确的结果,这个时候模型就训练好了。

机器学习的模型有很多种,也就是各种成熟的算法,包括决策树、随机森林、逻辑回归、SVM、朴素贝叶斯、随机森林、支持向量等。

它设计并开发算法和模型,使计算机系统能够自动学习和提高性能,而无需明确地编程规则。机器学习侧重于从数据中挖掘模式、进行预测和决策。

深度学习(DL)

深度学习是机器学习的一个特定领域,其灵感来源于人脑神经网络的结构。

机器学习的模型是一个不断发展的过程,后来人们逐渐研究出了一种更加智能和通用的模型,就是卷积神经网络(CNN)。

CNN 模拟人类大脑神经突触之间的连接,通过调整参数来模拟突触连接的强弱。

CNN 包含很多层,每一层又包含多个节点。除了第一层和最后一层,中间的那些统称为隐藏层(蓝色部分)。隐藏层可以多达数百层,每一层的输入都是上一层的输出,同时每一层的输出都可以作为下一层的输入,它们交织在一起就形成了一个很深的网络,所以称为“深度学习”。

除了 CNN,深度学习还有很多其它的衍生模型(算法),比如循环神经网络(RNN)、深度置信网络(DBN)、长短期记忆模型(LSTM)、生成对抗网络(GAN)、受限玻尔兹曼机(RBM)等。

它建立了一种称为深度神经网络的模型,该模型由多个层次组成,每个层次都通过学习从底层数据中提取更高级的特征表示。

深度学习在处理大规模数据和复杂任务时表现出色,如图像识别、语音识别和自然语言处理等。

简而言之,人工智能是一门广泛领域,旨在开发智能系统;机器学习是实现人工智能的方法之一,通过从数据中学习并改进性能;深度学习是机器学习的一个分支,使用深层神经网络模型来学习和提取复杂的特征表示。