学做古典家具网站做网站教程 简书

全文共分为两个部分:第一让苹果手机接入AI,第二是让苹果手机接入ChatGPT 4o功能。

一、国行版iPhone开通 Apple Intelligence教程

打破限制:让国行版苹果手机也能接入AI

此次发布会上,虽然国行 iPhone16 系列不支持 GPT-4o,但这并没有难倒充满热情的技术社区。

估摸着不少小伙伴们要冲,今儿给大家分享下国行 iPhone 手机开通 Apple Intelligence 干货教程,希望对你有帮助,总时长5min,不需要抹除手机原始数据。

前期准备

1、设备必须是 iPhone15 Pro、iPhone15 Pro Max,或者你即将入手的 iPhone16 ;

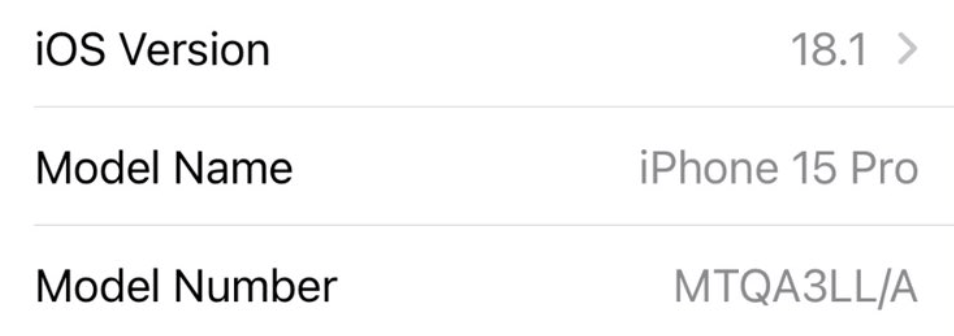

2、手机系统要升级到 18.1 Beta 及其以上(因为该版本才新增 Apple Intelligence,正式版预计要等到十月中旬)如果不行的话就反复尝试,重启手机;

3、准备好一个美区 Apple ID,确认关于本机的 Model Number 以 LL/A 结尾;

4、在 iPhone 设备上提前关闭定位查找我的 iPhone;

5、一台 Mac 或者 Windows 电脑 (另外,手机不需要挂梯z)

详细步骤

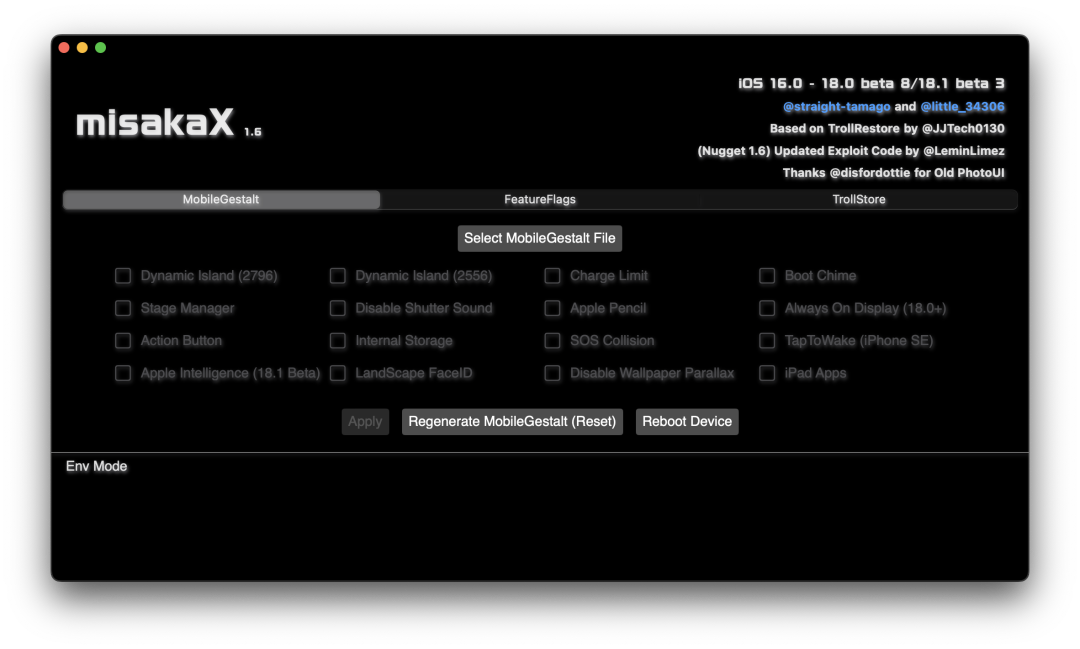

1、下载 MisakaX(http://t.cn/A6RHtIpI),在 release 里。(其中 Windows 版需要电脑上安装 iTunes)

地址:https://github.com/straight-tamago/misakaX

2、下载后把 App 移动到 Mac 应用程序文件夹里。

3、打开,点 “Intall pymobiledevices3”

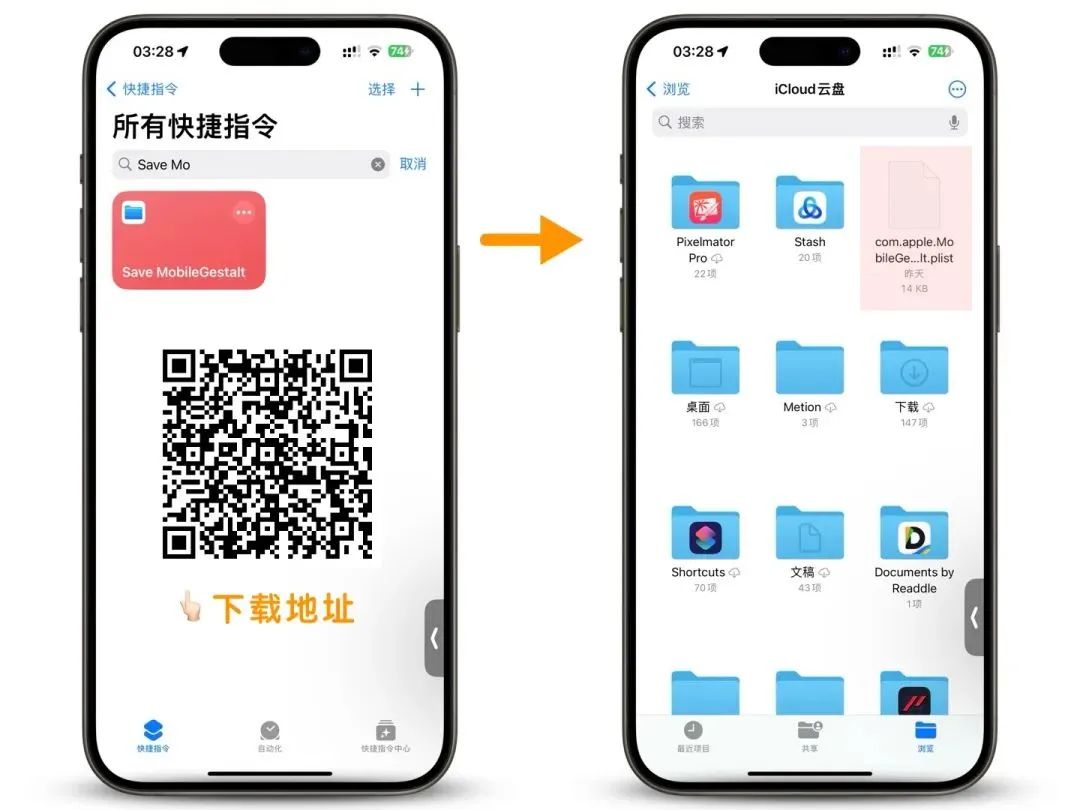

4、下载快捷指令:http://t.cn/A6RTC7cL,运行指令后导出 iPhone 配置文件给 Mac电脑/网盘.

5、iPhone 连接数据线到 Mac,信任计算机。

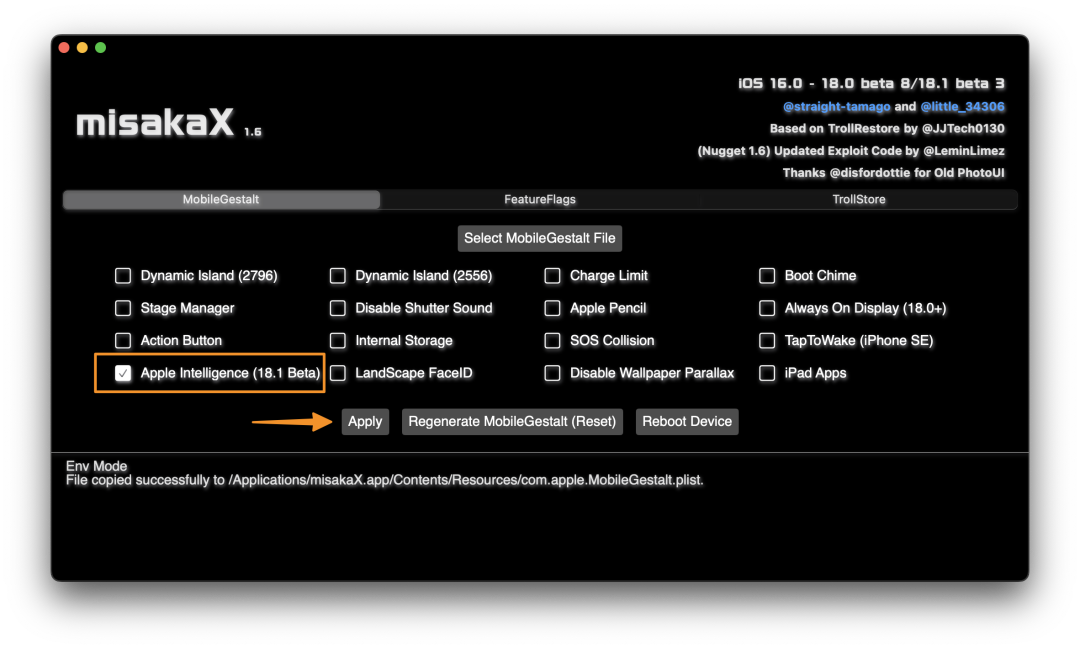

6、勾选设备版本,然后点击 MisakaX 的 Apply.

7、等待系统重启。重启后,有一个欢迎界面,按照指引完成设置,语言为英文,地区为美国(United States)。

出现 Apple ID 头像并询问你的偏好设置的时候,请选择 Customize,并在 Apps & Data 页面选择 "Don't Transfer Apps & Data"。

8、激活的时候选择【不要】抹掉。

9、进入系统后系统语言、地区、和 Siri 语言三个都改成美国,iCloud ID 登录美区的。

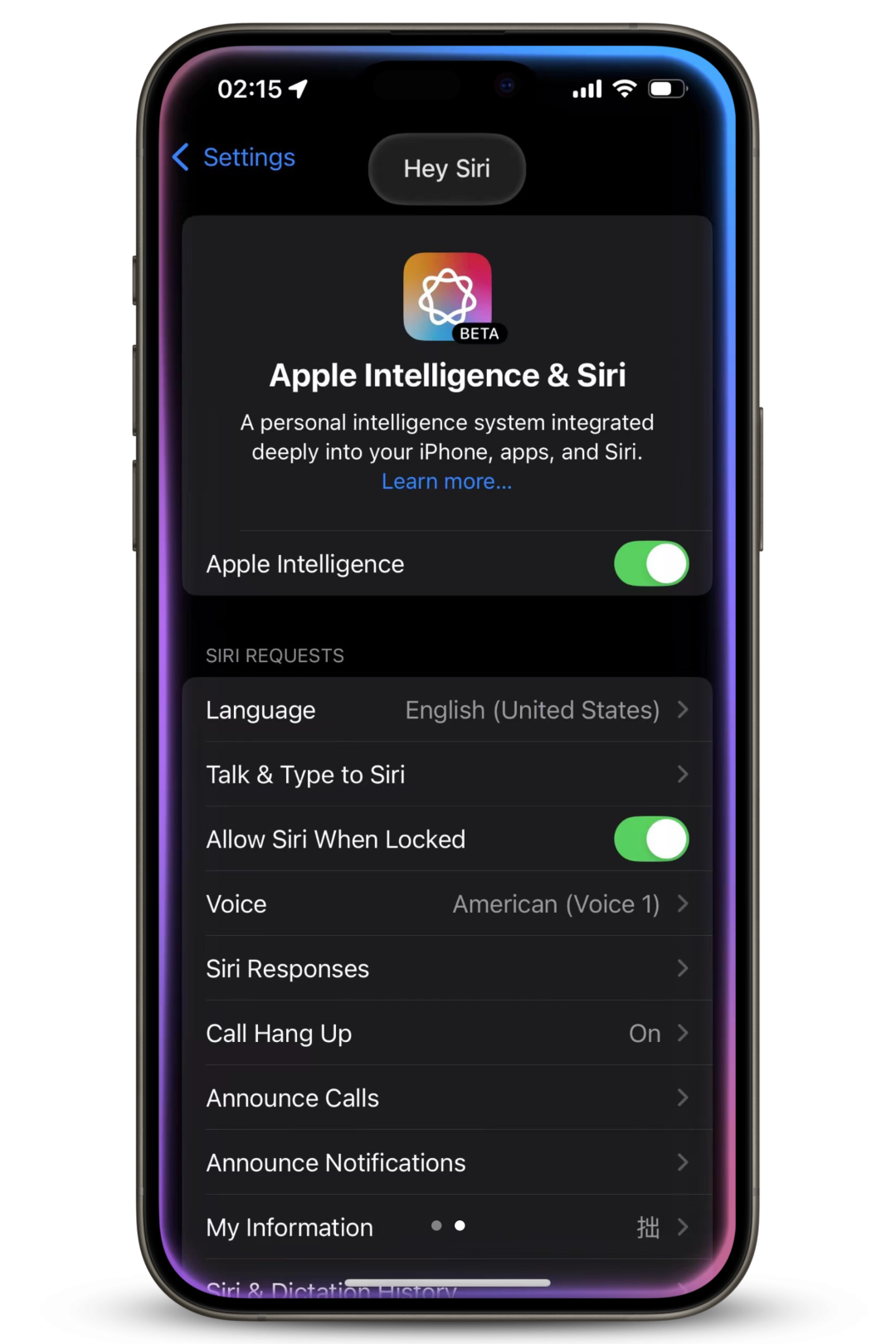

10、Siri 会提示加入 Apple intelligence 候选。

11、加入之后等十来分钟就可以使用了。

不过该说的风险咱还是要提醒一下各位友友,修改完你在关于本机查看,就会发现版本已经变成了 LL/A 结尾的美版 iPhone 了。

于是乎,这样就带来了风险,就是其是官方保修和二手贬值可能会受影响,请自行评估。

此外,目前ChatGPT 和表情创建等功能还未上线测试,目前唯一无障碍使用的估计就是就是照片清除功能,更多功能可能得等等明天的iPhone16发布会我们一起瞅瞅。

对了,如果你打算入手购买买即将发布的国行iPhone16,那么可得赶紧插个眼。不要交智商税。

二、国行版iPhone手机接入GPT-4o详细步骤

话不多说,今天我们就为大家带来一个详细的教程,让你的国行iPhone 通过几个简单步骤,也能丝滑接入 GPT-4o,畅想科技与狠活!

必须条件

-

一部 iPhone(任意型号,当然太老也不行)、或 iPad、MacBook

-

只要能够认识英文字母,无需科技上网

-

有效的 GPT-4o API key,买一次,能用大半年不止

请打开你尊贵的 iPhone,开始操作

-

第一步、安装快捷指令

使用 iPhone 自带的 Safari 浏览器,安装两个快捷指令:

1. 视觉

https://www.icloud.com/shortcuts/5b48a73552c045d6885e70507fd7d5e2

2. 语音

https://www.icloud.com/shortcuts/e0bc5445c39d45a78b90e1dc896cd010

-

第二步、获取并配置 API Key

打开快捷指令,输入API Key。这是连接 GPT-4o 的关键,每个用户的 API Key都是独一无二的(通常以“sk-”开头)。

获取 API Key 推荐地址:https://shop.hkgpt.top/shop/46(也可以通过官方注册购买)

请妥善保管你的 API Key,避免泄露。

-

第三步、测试运行指令

安装和配置完成后,首次运行快捷指令时,请按照提示点击“允许访问”或“是”,确保一切设置无误。

充分发挥 GPT-4o 强大功能

-

拍照识别

使用 GPT-4o 分析和解读图像内容,如文字识别、物体识别等。

-

语音助手

从 Siri 中与 GPT-4o 沟通

结语:9月10日我们迎来了 iPhone16 系列的发布,GPT-4o 的深度集成让新款 iPhone 具备了前所未有的智能对话、实时翻译、智能推荐等强大功能。但令人遗憾的是,中国地区的果粉们无缘。根据苹果官方信息,Apple 智能目前还不适用于国行版 iPhone。这意味着,即使你手中握有最新的 iPhone 16,仍然无法享受这项功能。[已经习惯了苹果每次发布会都会针对不同地区特殊对待>_<]

好了,今天就分享到这儿。如果觉得本文对大家有帮助请不要忘记点赞和转发哦~!